#### PREMIO TESI DI DOTTORATO

**− 58 −**

#### PREMIO TESI DI DOTTORATO

#### Commissione giudicatrice, anno 2015

#### Vincenzo Varano, presidente della Commissione

Tito Arecchi, Area scientifica

Aldo Bompani, Area Scienze Sociali

Franco Cambi, Area Umanistica

Paolo Felli, Area Tecnologica

Michele Arcangelo Feo, Area Umanistica

Roberto Genesio, Area Tecnologica

Mario Pio Marzocchi, Area Scientifica

Adolfo Pazzagli, Area Biomedica

Giuliano Pinto, Area Umanistica

Salvatore Ruggieri, Area Biomedica

Saulo Sirigatti, Area Biomedica

Fiorenzo Cesare Ugolini, Area Tecnologica

Graziella Vescovini, Area Umanistica

# Study and design of topologies and components for high power density DC-DC converters

Study and design of topologies and components for high power density DC-DC converters / Giacomo Calabrese. – Firenze: Firenze University Press, 2016. (Premio Tesi di Dottorato; 58)

http://digital.casalini.it/9788864533537

ISBN 978-88-6453-352-0 (print) ISBN 978-88-6453-353-7 (online)

Front cover design: Alberto Pizarro Fernández, Pagina Maestra snc

#### Peer Review Process

All publications are submitted to an external refereeing process under the responsibility of the FUP Editorial Board and the Scientific Committees of the individual series. The works published in the FUP catalogue are evaluated and approved by the Editorial Board of the publishing house. For a more detailed description of the refereeing process we refer to the official documents published on the website and in the online catalogue of the FUP (www.fupress.com).

Firenze University Press Editorial Board

G. Nigro (Co-ordinator), M.T. Bartoli, M. Boddi, R. Casalbuoni, C. Ciappei, R. Del Punta, A. Dolfi, V. Fargion, S. Ferrone, M. Garzaniti, P. Guarnieri, A. Mariani, M. Marini, A. Novelli, M.C. Torricelli, M. Verga, A. Zorzi.

This work is licensed under a Creative Commons Attribution 4.0 International License (CC BY 4.0: http://creativecommons.org/licenses/by/4.0/)

**CC** 2016 Firenze University Press Università degli Studi di Firenze Firenze University Press via Cittadella, 7, 50144 Firenze, Italy www.fupress.com *Printed in Italy*

To my parents Gaetano and Stefania

#### **Contents**

| Chapter 1                                                         |    |

|-------------------------------------------------------------------|----|

| Introduction                                                      | 13 |

| 1.1 Switching frequency increment                                 | 14 |

| 1.2 Semiconductor materials                                       | 16 |

| 1.3 Passive components                                            | 18 |

| 1.3.1 Inductors                                                   | 18 |

| 1.3.2 Capacitors                                                  | 19 |

| 1.4 Converter topologies                                          | 21 |

| 1.4.1 High frequency power conversion                             | 21 |

| 1.4.2 Very high frequency power conversion                        | 22 |

| 1.5 Thesis structure and contribution                             | 23 |

| Chapter 2                                                         |    |

| Integrated high step-down multiphase buck design                  | 27 |

| 2.1 Introduction                                                  | 27 |

| 2.2 High step-down multiphase buck operation analysis             | 29 |

| 2.2.1 Sequential high side switches turn-on: k=1 switching scheme | 29 |

| 2.2.2 Two-by-two high side switches turn-on: k=2 switching scheme | 34 |

| 2.3 Comparison with multiphase buck                               | 35 |

| 2.4 Functional overview of the implemented converter              | 38 |

| 2.4.1 Passive components sizing                                   | 40 |

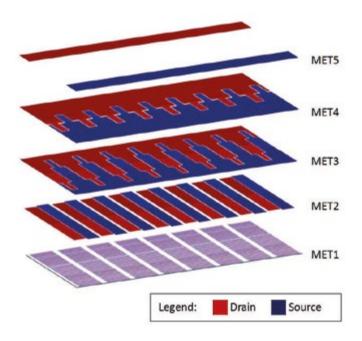

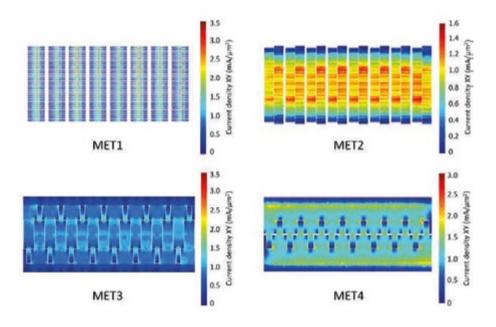

| 2.5 Power stage                                                   | 41 |

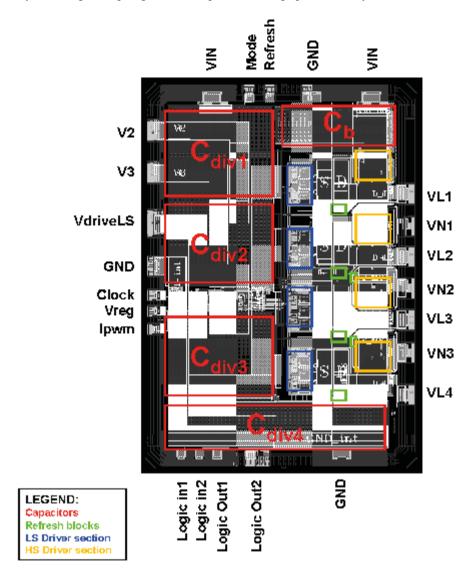

| 2.5.1 Layout                                                      | 41 |

| 2.5.2 High side's switches source and drain connections design    | 42 |

| 2.6 Drive architecture                                            | 42 |

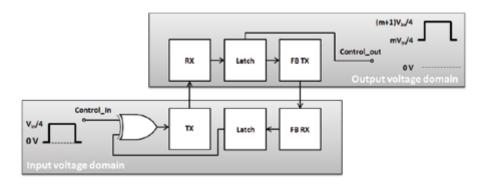

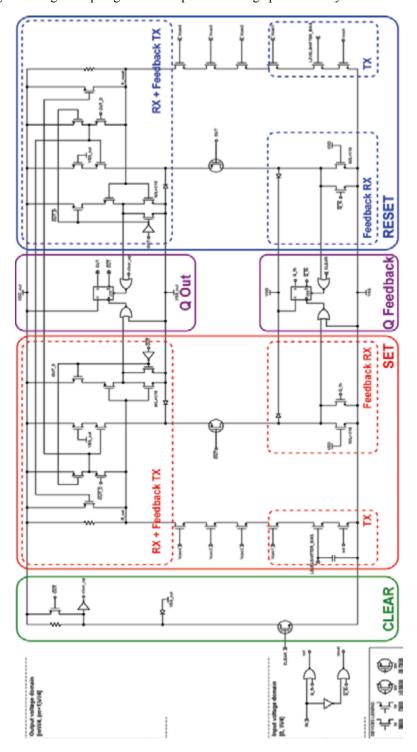

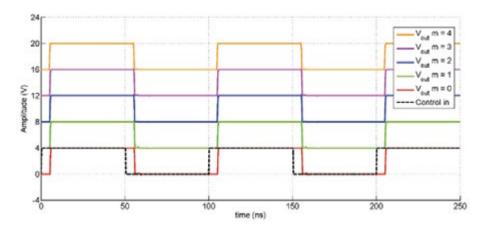

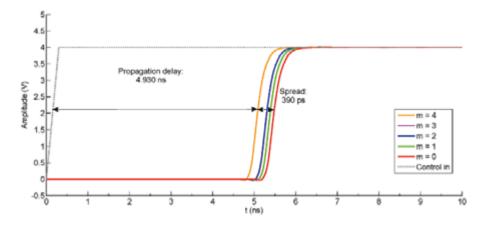

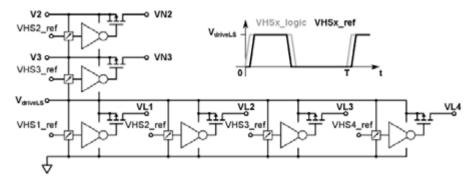

| 2.6.1 Architecture overview                                       | 43 |

| 2.6.2 Driver sections "selective" tapering                        | 45 |

| 2.6.3 Level shifter                                               | 46 |

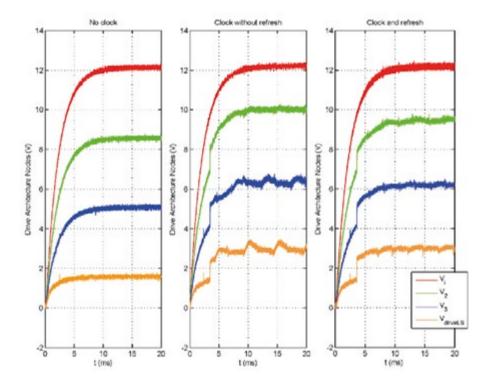

| 2.6.4 Refresh architecture                                        | 48 |

| 2.6.5 Layout                                                      | 50 |

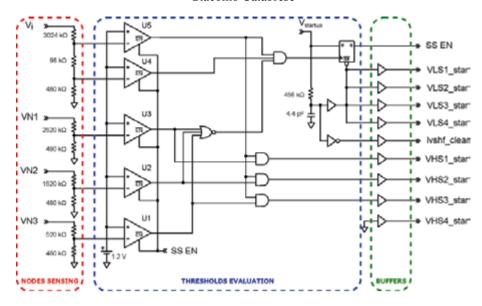

| 2.7 Start-up logic                                                | 50 |

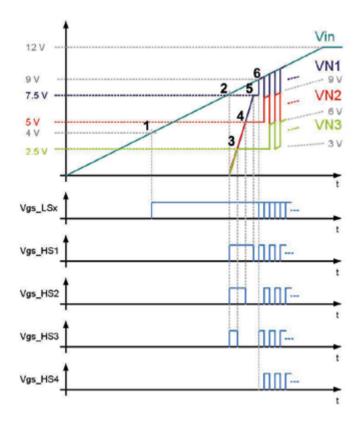

| 2.7.1 Start-up sequence                                           | 51 |

| 2.7.2 Start-up voltage supply                                     | 52 |

Giacomo Calabrese, *Study and design of topologies and components for high power density dc-dc converters*, ISBN 978-88-6453-352-0 (print) ISBN 978-88-6453-353-7 (online) **CC** BY 4.0, 2016 Firenze University Press

| Study and design of topologies and components for high power density DC-DC co | onverters |

|-------------------------------------------------------------------------------|-----------|

| 2.8 Steady-state operation                                                    | 52        |

| 2.8.1 Steady-state logic                                                      | 52        |

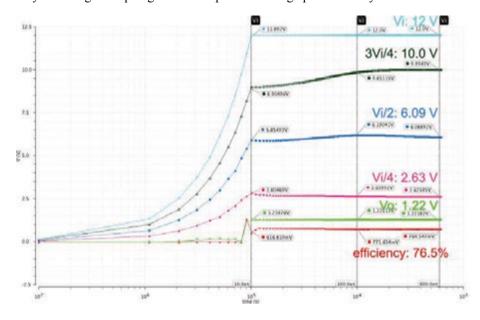

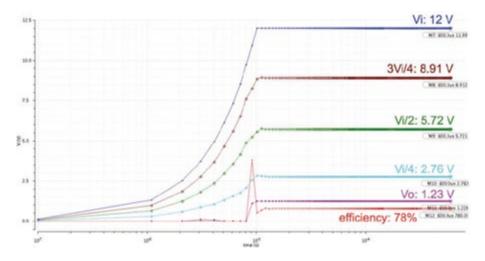

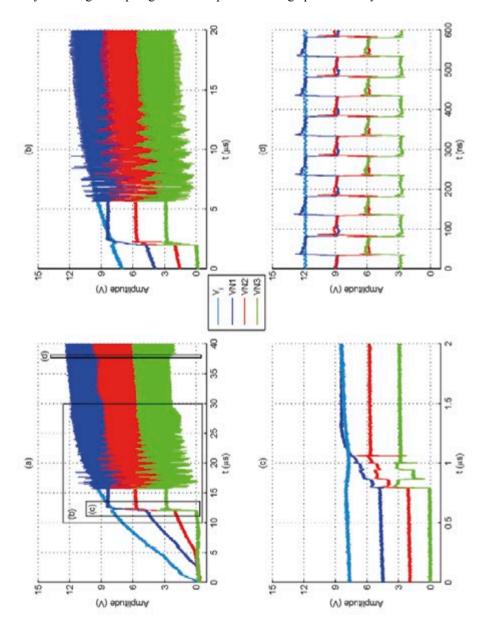

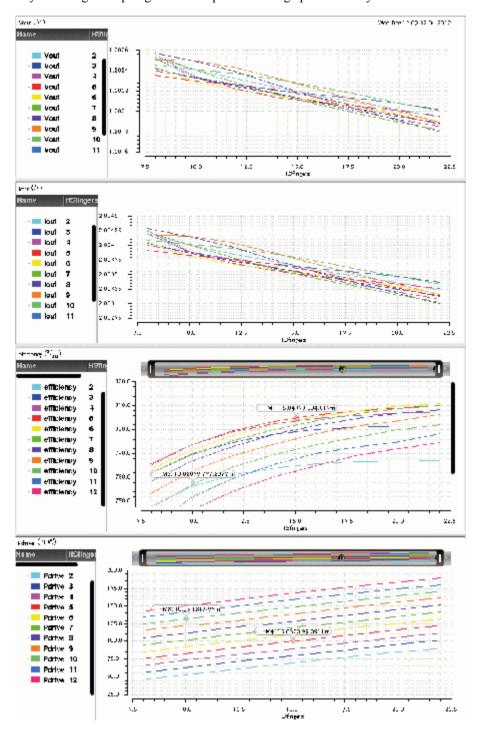

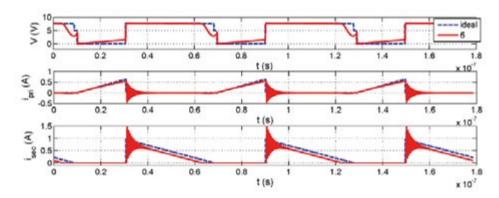

| 2.9 Simulation results                                                        | 55        |

| 2.9.1 Parasitics modeling in circuital simulations                            | 56        |

| 2.9.2 Optimization of power switches sizing                                   | 56        |

| 2.9.3 Optimal disoverlap analysis                                             | 58        |

| 2.9.4 Start-up transient analysis in technological process corners            | 59        |

| 2.9.5 Power losses breakdown and efficiency evaluation                        | 59        |

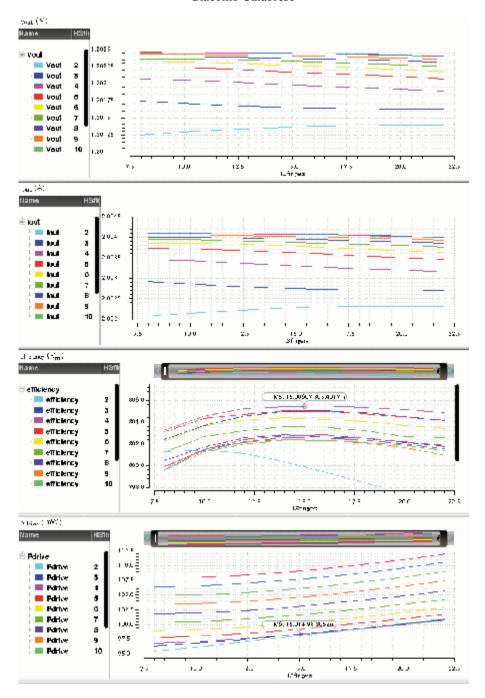

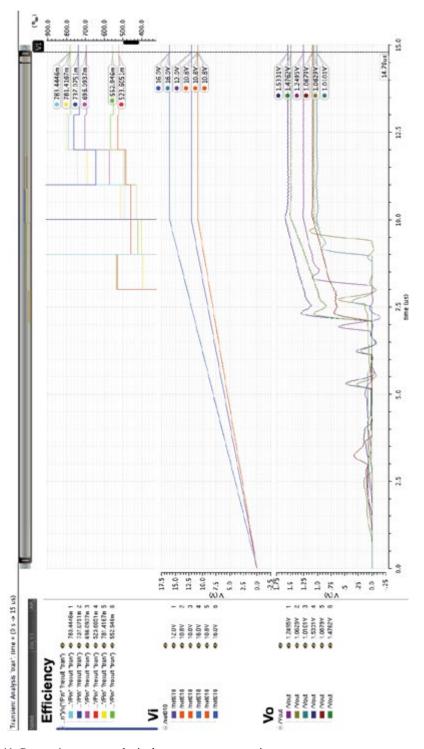

| 2.9.6 Efficiency                                                              | 60        |

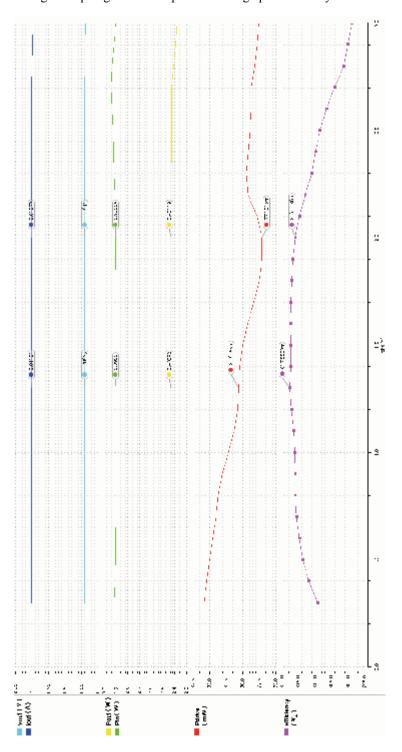

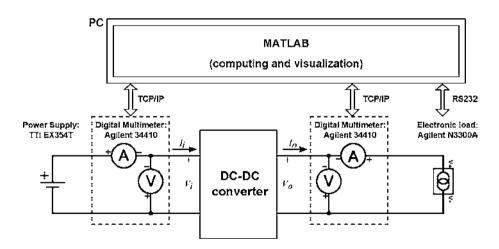

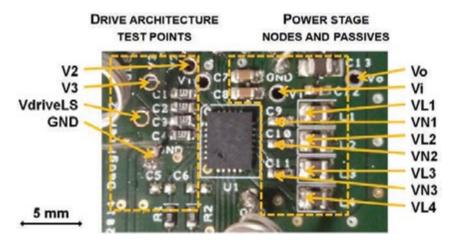

| 2.10 Board design and measurement results                                     | 61        |

| 2.10.1 Power stage voltage waveforms                                          | 61        |

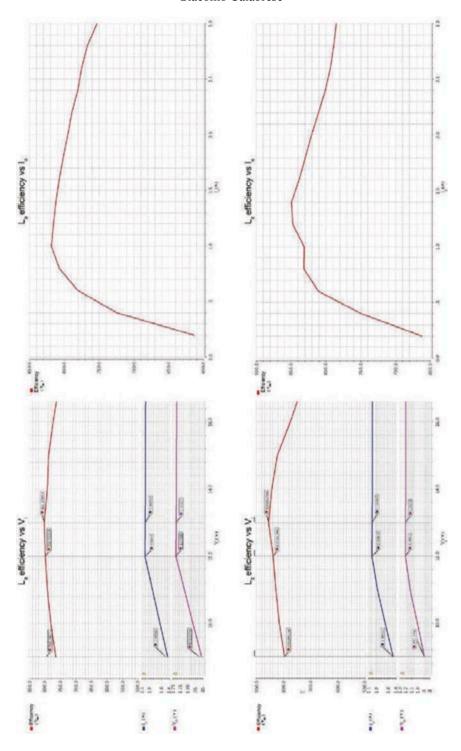

| 2.10.2 Efficiency                                                             | 62        |

| 2.11 Power density comparison                                                 | 63        |

| 2.12 Conclusion                                                               | 64        |

| Chapter 3                                                                     |           |

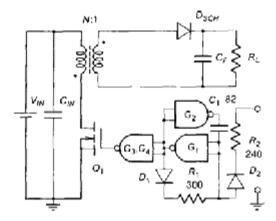

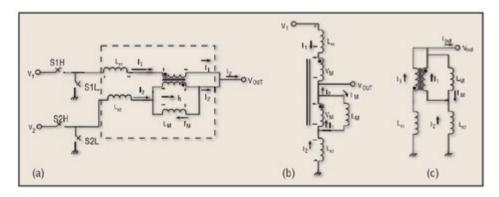

| High power density stackable flyback architecture                             | 105       |

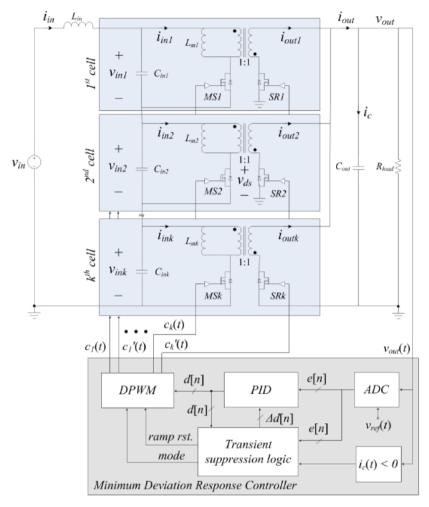

| 3.1 Topology overview                                                         | 105       |

| 3.1.1 Minimum deviation controller                                            | 106       |

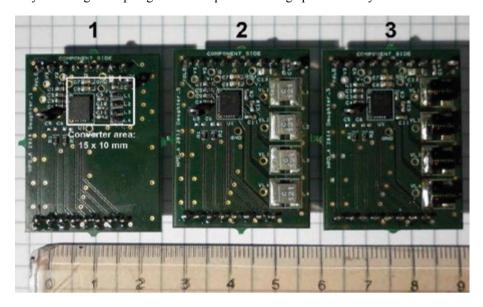

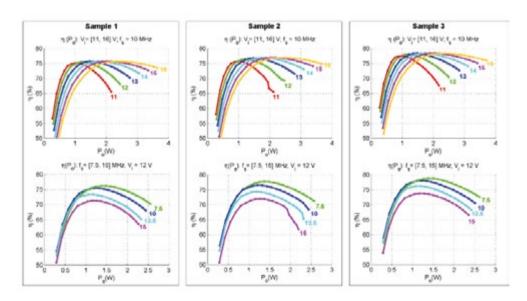

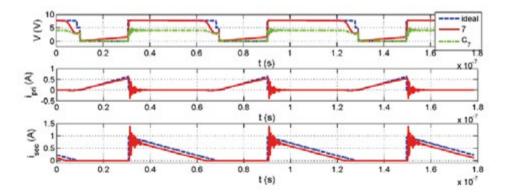

| 3.2 Miniaturization of the stackable flyback                                  | 106       |

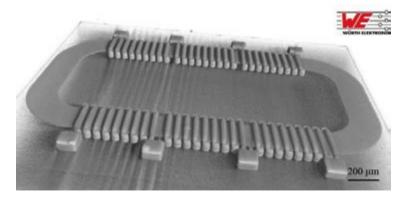

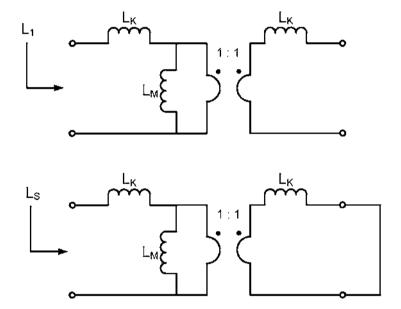

| 3.3 Integrated micro-transformer                                              | 108       |

| 3.4 Overview on HF flyback design                                             | 109       |

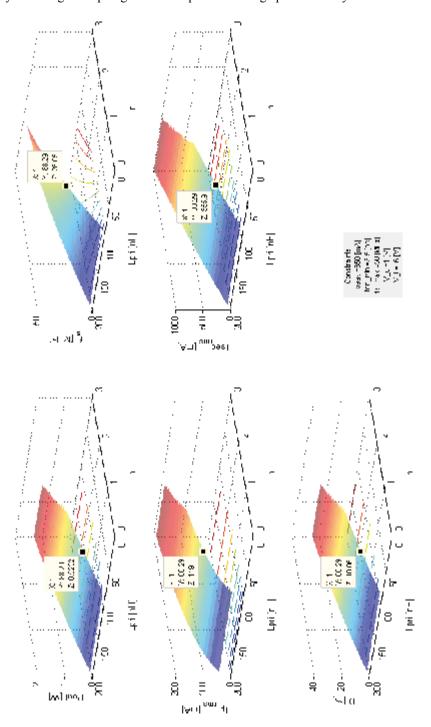

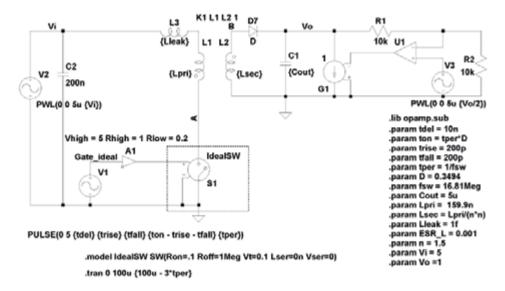

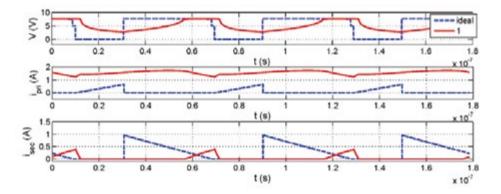

| 3.5 Micro-transformer preliminary simulation                                  | 111       |

| 3.6 Transformer optimization script                                           | 112       |

| 3.6.1 Model degrees of freedom, constraints and outputs definition            | 112       |

| 3.6.2 Testing of the model                                                    | 115       |

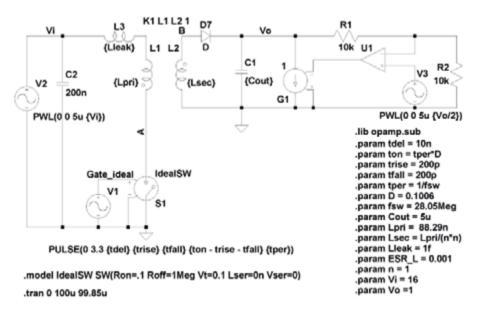

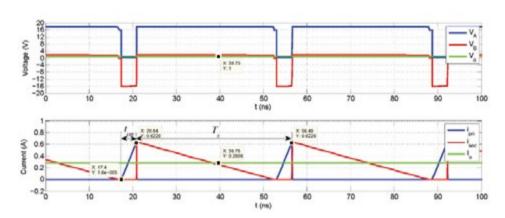

| 3.7 Considerations on discrete components prototype design                    | 116       |

| 3.7.1 Estimation of parameters                                                | 117       |

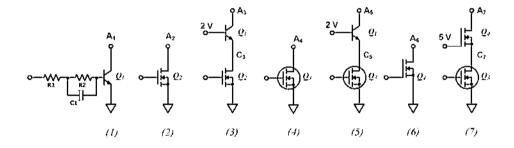

| 3.7.2 Evaluation of different solutions for main switch                       | 118       |

| 3.8 Conclusion                                                                | 122       |

### 10

135

135

136

137

Chapter 4

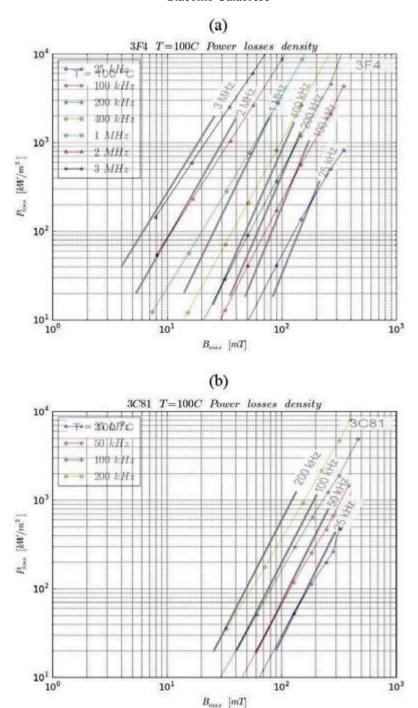

Hysteresis core losses model

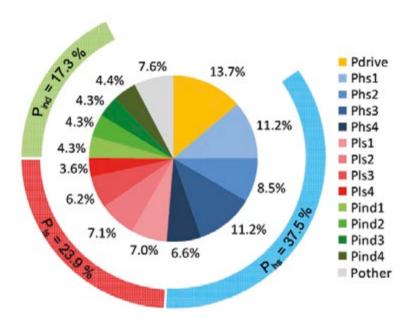

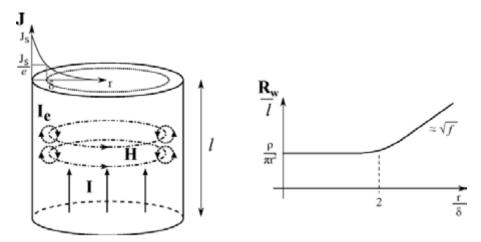

4.1 Power losses contributions

4.1.1 Conductor losses

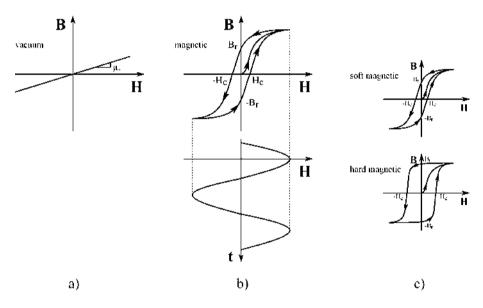

4.1.2 Core losses

| 4.2 Overview on magnetic materials' power losses models  | 140 |

|----------------------------------------------------------|-----|

| 4.2.1 Small signal models                                | 140 |

| 4.2.2 Large signal models                                | 141 |

| 4.2.3 Conclusion                                         | 143 |

| 4.3 Jiles-Atherthon Hysteresis model                     | 144 |

| 4.3.1 Anhysteretic magnetic permeability                 | 144 |

| 4.3.2 Irreversible differential susceptibility           | 145 |

| 4.3.3 Reversible differential susceptibility             | 145 |

| 4.3.4 Total differential susceptibility                  | 146 |

| 4.3.5 Time domain model                                  | 146 |

| 4.3.6 Material parameters                                | 147 |

| 4.3.7 Frequency dependency                               | 148 |

| 4.4 Model implementation and results                     | 149 |

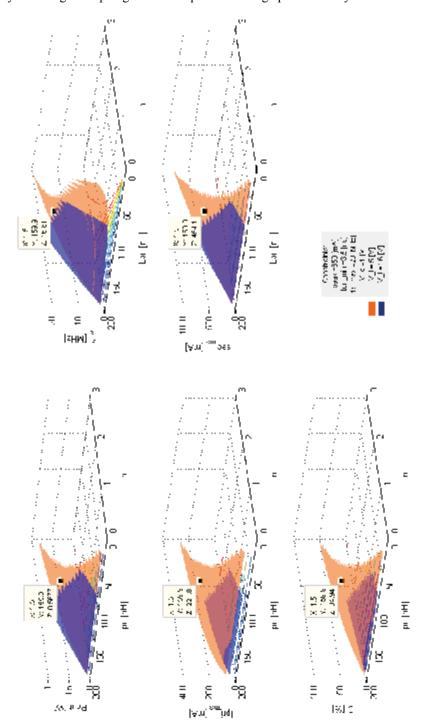

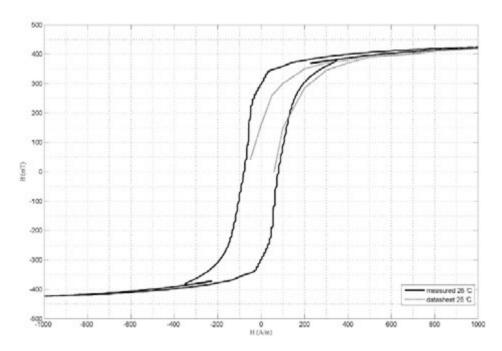

| 4.4.1 Full saturation hysteresis loop                    | 149 |

| 4.4.2 Loop plots for various current waveforms           | 149 |

| 4.4.3 Core losses density estimation                     | 150 |

| 4.5 Conclusions                                          | 151 |

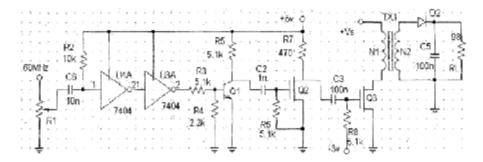

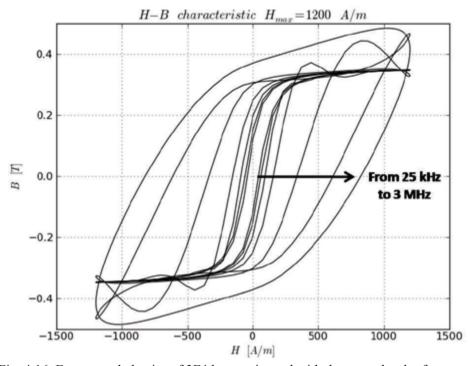

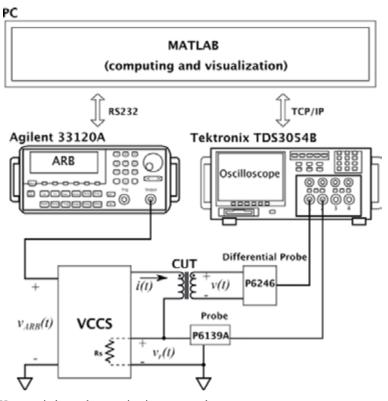

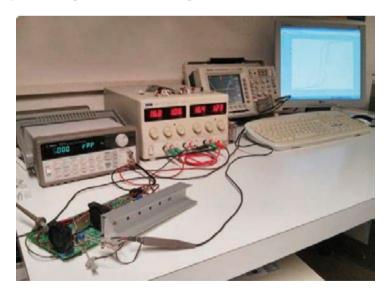

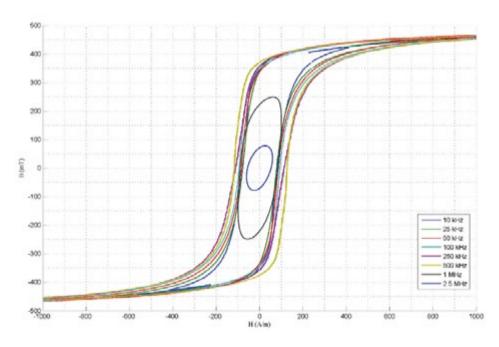

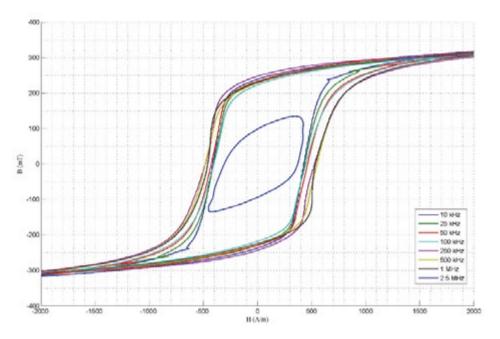

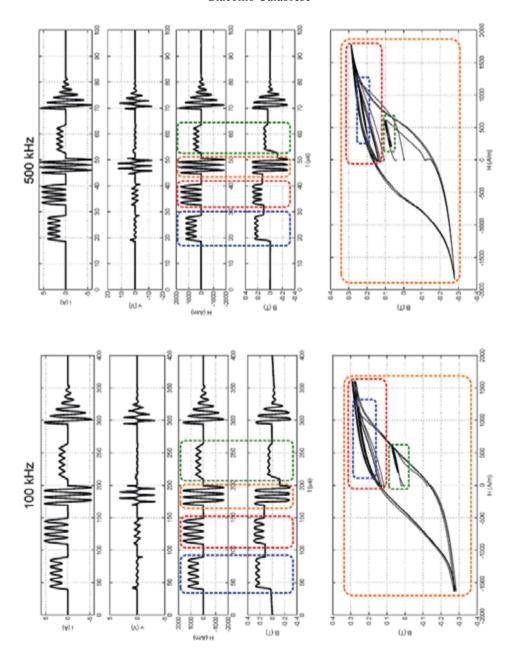

| Chapter 5 Hysteresis measurement setup                   | 161 |

| 5.1 System overview                                      | 162 |

| 5.1.1 Magnetic hysteresis measurement principle          | 162 |

| 5.1.2 Setup description                                  | 163 |

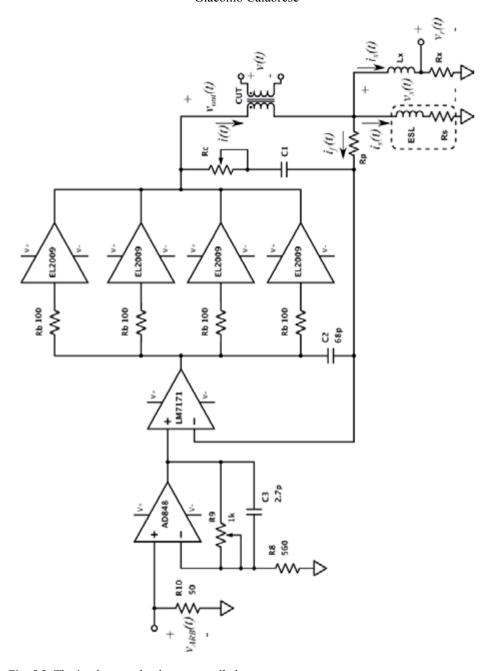

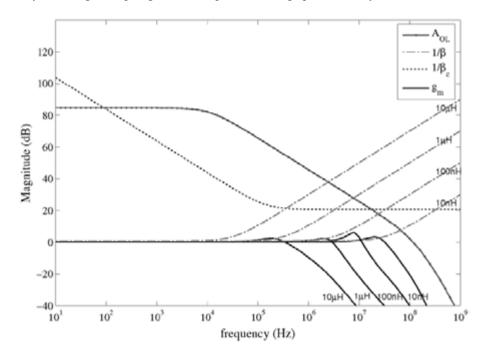

| 5.1.3 Voltage Controlled Current Source                  | 164 |

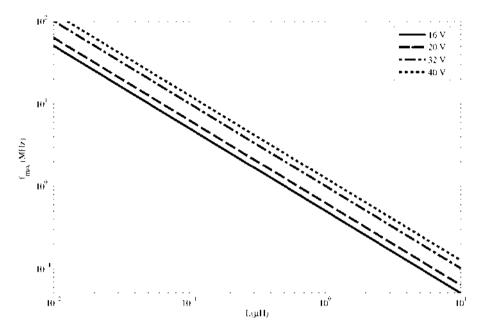

| 5.1.4 Setup performance boundaries                       | 166 |

| 5.1.5 Phase delay errors evaluation                      | 167 |

| 5.1.6 Current sensing network design                     | 167 |

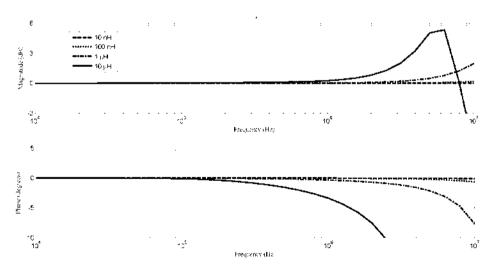

| 5.1.7 VCCS transconductance measurement                  | 169 |

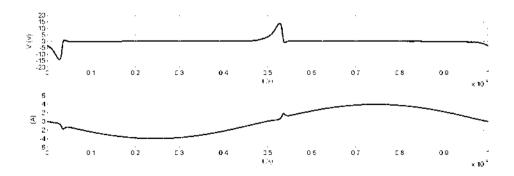

| 5.2 Results                                              | 169 |

| 5.2.1 Ferrite materials test samples                     | 169 |

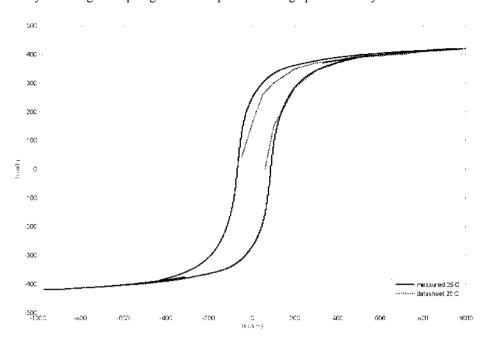

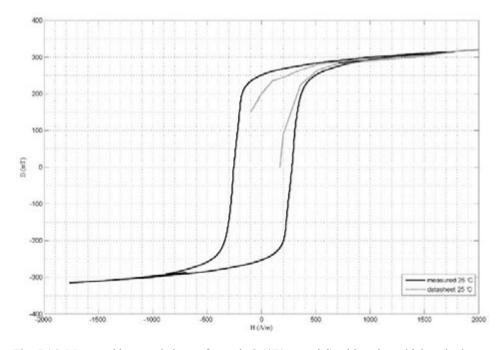

| 5.2.2 Hysteresis loop characterization of magnetic cores | 170 |

| 5.2.3 Frequency behaviour                                | 171 |

| 5.2.4 Test signal with multiple waveforms and DC bias    | 171 |

| 5.2.5 Temperature dependence of hysteresis loop          | 172 |

| 5.3 Conclusions                                          | 172 |

| Chapter 6 Conclusions and future work                    | 185 |

#### Study and design of topologies and components for high power density DC-DC converters

| Appendix A Ripple reduction comparison                      | 189 |

|-------------------------------------------------------------|-----|

| A.1 Buck                                                    | 189 |

| A.2 Multiphase interleaved buck                             | 190 |

| A.3 Multiphase interleaved buck with coupled inductances:   | 192 |

| A.4 Comparison                                              | 195 |

| A.5 Conclusion                                              | 197 |

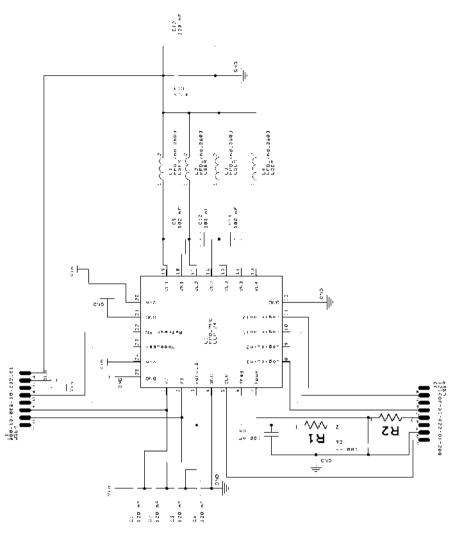

| Appendix B Test chip boards schematics                      | 205 |

| Appendix C High frequency flyback transformer sizing script | 209 |

| Bibliography                                                | 213 |

| Acknowledgements                                            | 221 |

## Chapter 1 Introduction

Switching power converters are receiving considerable research attention in terms of size reduction while preserving, or increasing, the quantity of output power and the conversion efficiency they can provide. This attention is directly generated by the need of reducing the volume occupation in electronic systems directly addressable to power management. In fact, power management is often considered as a "ghost" functionality which is always necessary but should affect as minimum as possible the overall system requirements. In terms of occupied volume, this directly translates to the consideration that if the one occupied by power management can be reduced, there will be more space for adding functionality or simply to miniaturize the overall system.

This is mostly evident in consumer portable electronic devices, where this approach has contributed, together with the developments in other areas of electronics, to the possibility of adding several functional blocks without increasing the overall system's volume with respect to what was achievable in the past. As a consequence, this increased functionality, has led to a need of several different power rails which must supply different blocks such as CPUs, RF power amplifiers, displays, sensors and devices like cameras and lights.

Each of these blocks has very different requirements in terms of supply voltage, power, regulation and transient response. At the same time, in order to have an efficient power management which minimizes losses and parasitics, each of them requires its power supply to be as close as possible. Moreover, this increased complexity of the power management systems should have a minimum possible impact on overall system reliability and cost.

The challenges in power management mentioned above, have shifted the development of power supplies from solutions made of assembled discrete components towards solutions based on integrated power semiconductors. Initially, solutions were based on an integrated controller with external power switches, while nowadays are commonly available single power management integrated circuit (PMIC) systems which requires only few external passive components. In this evolution, integrated power electronics products, ranging from single power switches to very complex integrated power management solutions, have become one of the key market segments of many semiconductor companies and a main research topic for academic professionals working in power electronics.

When considering the miniaturization of a power converter, it is often required to maintain or increase the output power provided with previous solutions. It is often

Study and design of topologies and components for high power density DC-DC converters

possible to consider a certain power density value as a target parameter to improve. Power density is given as a ratio of output power over converter volume and together with conversion efficiency is a key parameter in miniaturization. The road-map for increasing power density is now moving from converters using single PMIC systems with external passive components to the so-called "Power Supply in Package" (PwrSiP), where the passive components are placed inside the same package of the PMIC. As a further step towards the miniaturization, the "Power Supply on Chip" (PwrSoC) [1] has passive components which are directly realized on the same die of the PMIC by means of stacking or direct monolithic integration.

For this aim, the size of passive components needs to be reduced. The principal way to reduce the size of passives is by reducing their required inductance and capacitance values which are, on a first approximation, directly proportional to the amount of energy storage required. As it will be briefly recalled in section 1.1, in order to reduce the energy storage, the switching frequencies of the new proposed power conversion solutions are increased, typically in the range from 1 MHz to 100 MHz. This increase usually provides a faster response to transients and the values of required passive components can be decreased by one or two orders of magnitude allowing new miniaturization possibilities. As drawbacks, switching losses are increasing with switching frequency requiring their careful analysis to achieve good efficiency, while implementation and control also requires additional attention.

For these reasons, the power density enhancement of DC/DC converters is driven by three main research areas which are closely related to each other. These are:

- semiconductor materials and devices;

- passive components;

- converter topologies and control.

In section 1.1 the principle behind the benefit related to the switching frequency increase will be reviewed. Sections 1.2, 1.3 and 1.4 will give additional details with respect to the main topics of the different research areas of interest mentioned above. Section 1.5 will outline the structure and aim of this dissertation.

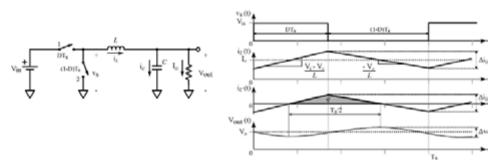

#### 1.1 Switching frequency increment

An ideal switching converter topology is composed of three circuital component types: switches, inductors and capacitors. Resistors are unwanted components due to their capability of dissipating real power. In order to understand how the passive components numerical values can be reduced, without modifying the input to output voltage transfer function, we can use the buck converter topology shown in Fig. 1.1 as an example. In this case, the resistor is used to model the load power absorption. The principle of operation of the most common switching converter topologies, including buck, can be found in [2] together with the techniques developed for their circuital analysis.

Briefly, the switches are alternatively turned on with a switching period:

$$T_s = \frac{1}{f_s} \tag{1.1}$$

where  $f_s$  is the switching frequency of the converter. The fraction of the period associated to the turn-on time of switch 1, connected to the input, is called duty cycle D and is defined as:

$$D = \frac{t_{on 1}}{T_s}. ag{1.2}$$

The rest of the period is associated to the turn-on time of switch 2.

This behavior produces the waveform  $v_s(t)$ , shown in Fig.1.1, for the voltage at the switching node. The L and C are basically a non dissipative filter used to extract the average of  $v_s(t)$  on a switching period, such that the output voltage  $V_{out}$  is defined as:

$$V_{out} = \frac{1}{T_s} \int_{0}^{T_s} v_s(t) dt = \langle v_s \rangle_{T_s} = DV_{in}.$$

(1.3)

Ideally the output value is a constant voltage  $V_o$  proportional to the input voltage through a regulation set by the value of D. However, the L-C filter is not capable of completely separate the DC average of  $v_s(t)$  from its frequency components and some residual ripple  $\Delta v$  will still be present in the output voltage  $V_{out}$ . Its dominant component is the first harmonic of the switching frequency as shown in Fig. 1.1, where its amplitude has been exaggerated to underline the phenomena.

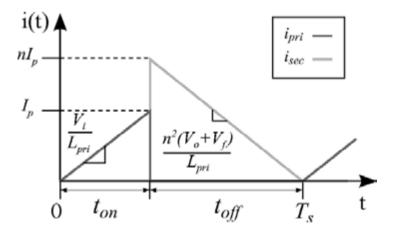

In order to quantify the amount of residual ripple in  $V_{out}$  we can start considering the inductor current  $i_L(t)$  shown in Fig. 1.1. In steady state, this current has a DC component which is set by the load absorption  $i_o$  and a ripple  $\Delta i_L$  given by the voltage swings seen by the inductor. For instance:

$$\Delta i_L = \frac{V_{in} - V_{out}}{L} DT_s = \left| -\frac{V_{out}}{L} (1 - D) T_s \right|. \tag{1.4}$$

If we revert equation 1.4 in order to obtain the sizing of inductance value we have:

$$L = \frac{V_{in} - V_{out}}{\Delta i_L} DT_s \tag{1.5}$$

where the  $\Delta i_L$  typically has values in the range of 10 to 20% of the full-load output current [2] in order to maintain reasonably low peak currents through the switches and constrain losses in magnetic core inductors as we will see later on.

While the DC value of the inductor current  $I_o$  flows through the load, the triangular ripple  $\Delta i_L$  should ideally flow through the capacitor. Under this assumption, the capacitor current  $i_C(t)$  looks like the waveform of Fig. 1.1. In steady state, during one switching period the capacitor stores and transfers the same amount of charge q for a zero net balance over the period.

Study and design of topologies and components for high power density DC-DC converters

Thus q, which corresponds to the grey highlighted area under  $i_C(t)$  is:

$$q = C \cdot \Delta v = \frac{1}{2} \cdot \frac{\Delta i_L}{2} \cdot \frac{T_s}{2} \tag{1.6}$$

such that the output voltage ripple can be obtained as:

$$\Delta v = \frac{\Delta i_L T_s}{8C}.\tag{1.7}$$

The output ripple is reduced to zero for C which tends to infinity, thus a residual ripple will always persist. Moreover, additional ripple related to the equivalent series resistance of non-ideal capacitors should also be considered. Usually the output ripple is specified with values around few points percent with respect to  $V_{out}$ , depending on which type of load should be supplied.

Looking at equations 1.4 and 1.7 it is possible to notice how, maintaining the same specifications on  $\Delta i_L$  and  $\Delta v$  required by a specific design, the values of L and C can be reduced by increasing the switching frequency. The nominal value of the passive components can be considered, in first approximation, as linearly dependent to their geometrical size. This explains why the switching frequency increase is an important factor for converters' size miniaturization.

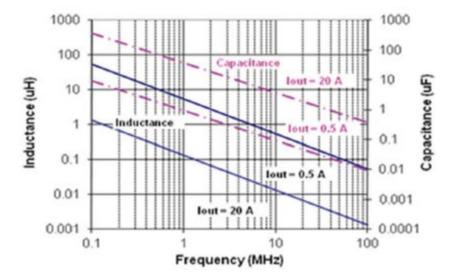

An interesting example related to a buck converter, showing the variation of L and C nominal values with increasing switching frequency, has been presented in [1] and is reported for completeness in Fig. 1.2. The values shown are estimated considering a basic set of specifications with  $V_{in} = 5 V$ ,  $V_{out} = 1 V$ ,  $\Delta i_L = 0.3 i_o$ ,  $\Delta v = 0.02 V_o$ .

However, increasing the switching frequency requires cautious considerations with respect to the increment of switching losses related to switches and passives non-ideal behavior. These limits are addressed by different research areas and will be briefly reviewed in the following sections.

Still looking at equations 1.4 and 1.7 it is worth to mention that we could also reduce the values of L and C by reducing the  $V_{in}$  -  $V_{out}$  term which directly maps the voltage difference applied to inductor. Obviously, one cannot freely change the  $V_{in}$  and  $V_{out}$  in a buck converter because they are usually specifications and not design parameters, but this idea is exploited by many modified topologies as we will treat also in this thesis.

#### 1.2 Semiconductor materials

Semiconductor devices used in converters switching at high frequencies should be capable of switching at high speed while presenting low on resistance. However, when considering a specific semiconductor technological process, these properties are inversely proportional due to the physical realization of the semiconductor devices.

The main loss contributions for a power switch are related to the presence of parasitics directly associated to their implementation. These usually cause a loss of

energy to turn on and off the switches, a loss of energy due to non-instantaneous turn on/off of the switches (current and voltage overlap at switching transitions) and phenomena of capacitive discharge [3, 4].

If we consider as an example, a MOSFET device, its drain to source on resistance  $R_{dson}$  is inversely proportional to its channel width. Once the value of  $R_{dson}$  is fixed, the conduction losses will be proportional to this value, independently of the switching frequency. In fact, it is possible to approximate the RMS value of the current as constant while increasing the switching frequency and maintaining the same ripple and power specifications.

The most straightforward way to minimize the conduction losses could seem the minimization of  $R_{dson}$  increasing the channel width. At the same time, the larger the channel width is, the higher is the parasitic capacitance seen from gate. This capacitance is often modeled as the input capacitance measured with drain and source short circuited:  $C_{ISS} = C_{ds} + C_{gs}$ . The charge required to charge this capacitance in order for the switch to turn on, is defined as gate charge  $Q_g$  and is directly proportional to the input capacitance. It follows that the power dissipated on gating  $P_g$  can be defined as:

$$P_q = Q_q V_{cc} f_s, (1.8)$$

where  $V_{cc}$  is the driver supply voltage. The gating losses are higher when the channel width is higher, thus they directly oppose to the minimization of the switch's  $R_{dson}$ . Moreover, they increase linearly with switching frequency.

With respect to the current and voltage overlap loss contribution, which causes another part of the switching losses, we can estimate that:

$$P_{ov} = K(t_r + t_f)V_{ds}I_{ds}f_s \tag{1.9}$$

where K is a factor between 1/6 and 1/2 while  $t_r$  and  $t_f$  are the MOSFET rise and fall times [3].

With respect to the capacitive discharge of the switch output at turn on we have to consider the  $C_{ds}$  capacitance which gives:

$$P_{cap} = \frac{1}{2} C_{ds} V_{ds}^2 f_s. {(1.10)}$$

There are different ways to minimize these contributions. A first solution is by acting on the voltages and currents applied to the switch at turn on and turn off in order to provide a "soft switching" transition. Techniques like the "zero voltage switching" (ZVS) or "zero current switching" (ZCS) aim to reduce to zero respectively the voltage or the current of the switch, by exploiting a resonance arranged within the converter passive components and some parasitic capacitance or inductance of the switches, or by properly adding passive elements. ZVS switching is preferred for the MOSFET because it aims at reducing both the overlap and capacitive discharge losses contribution. The idea of resonance is also used to reduce gate drive losses by employing resonant gate drivers.

However, as frequency is pushed higher, the previous solutions are limited by the fact that the conventional power devices (i.e. Si based devices) are approaching their performance limitations, imposed by semiconductor material properties. For this reason, a second solution for minimizing the switching losses is to use semiconductor materials which provides an improved  $R_{dson} \cdot Q_{\sigma}$  figure of merit with respect to silicon. This usually means also reduced input and output capacitances. As explained in [5] it is possible to define a power-frequency product of semiconductor devices. This figure of merit shows how novel structure and wide band-gap semiconductor devices, such as silicon carbide (SiC) and gallium nitride (GaN) devices, achieve both low gate capacitances and resistances while maintaining low onresistances. Their high carriers' saturated drift velocity allows a higher transition frequency with respect to Si processes (i.e. 2 times for SiC and 2.5 times for GaN considering an equal gate length) and their higher electric breakdown field (i.e. roughly 5 times higher for SiC and roughly 6 times higher for GaN) allows an higher power handling capability. Thus, they provide better high frequency performances for power applications.

As a drawback, they are nowadays emerging technologies which are significantly more expensive than Si to implement. Moreover, to the best of our knowledge, they require fabrication steps which do not allow to implement on the same die both the power switches and additional analog and digital functional blocks required for a complete PMIC. For this reason, the role of silicon is still dominant in product and research designs aiming at cost sensitive and general purpose power solutions, while new semiconductor material devices are at the moment relegated to niche markets of some specific high-end applications.

#### 1.3 Passive components

#### 1.3.1 Inductors

Among passives, magnetic components, both inductors and transformers, are key parts of switching converters topologies and pose a significant challenge in terms of size reduction. The switching frequencies with the potential of size reduction with respect to current converters are in the range of 1 MHz to 100 MHz [1]. Below 100 MHz it has been shown that inductors with magnetic cores are still capable of obtaining the same inductance values of an air-core inductor but requiring a smaller volume (higher inductance density) [6, 7, 8] and they can also provide advantages in terms of EMI due to magnetic flux confinement.

However, the miniaturization of magnetic components has not reported any major breakthrough in the past years leaving the power inductors as the bulkiest components in switching converters. Various geometries are actually being studied focusing on key parameters such as a high inductance value per unit area, low DC resistance for high current capability, and high Q-factor, for high efficiency [9, 10]. Toroidal cores, which provides a geometrical advantage on magnetic field confinement, due to the closure of the core and its intrinsic symmetry, are very complicated to implement with planar processes used for IC fabrication. Techniques borrowed

from micro electro-mechanical systems (MEMS) are applied for the realization of both cores and windings [11]. Among the possible geometries, shapes which differ from the toroidal one are evaluated to obtain a more favorable compatibility with planar processes [12]. Among these ideas it is worth citing racetrack inductors [13, 14], techniques exploiting wire bonding for the winding [15, 16] and techniques using spiral inductors embedded in magnetic composite materials [17].

As we anticipated, the high inductance density still requires the use of magnetic materials which provide high magnetic permeability but, at the same time, must be capable of withstanding significant currents (few to tens of Amperes for low power DC-DC point of load converters), meaning significant magnetic fields, without incurring into saturation. In order to provide the required inductance at high frequency, new magnetic materials are being studied.

A key technical problem in the study of magnetic materials suitable for the realization of miniaturized inductors is the compatibility with integrated circuit realization techniques. In fact, magnetic materials are not easy to deposit in such a way that their magnetic properties are preserved after deposition or can be steadily controlled. A main problem seems to be related to ensuring a magnetic isotropy or anisotropy of the material, depending on the required geometry and application. Deposition techniques like electroplating are used for core manufacturing but cannot guarantee a controlled anisotropy of the magnetic material. On the other hand, sputtering has shown to provide a controlled anisotropy of the manufactured core when a proper mechanical fixture is used to force an external magnetic field during the deposition [18, 19]. This allows to realize cores with better properties in terms of linearity of inductance and saturation.

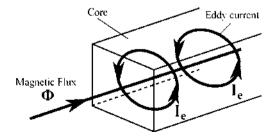

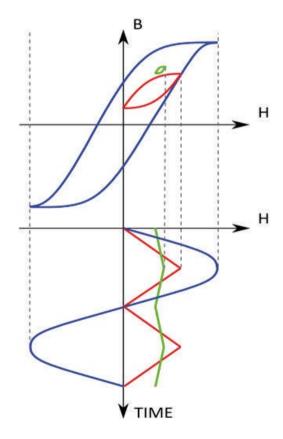

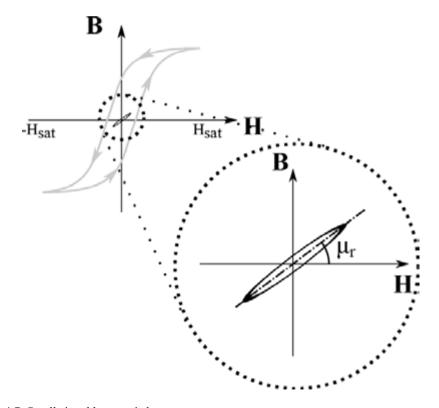

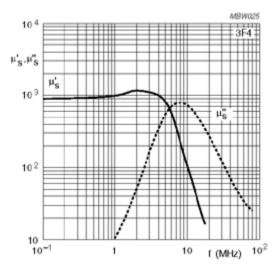

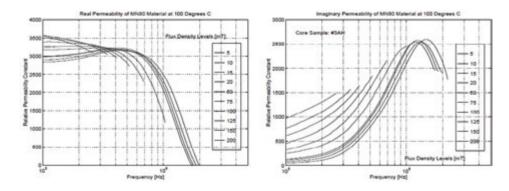

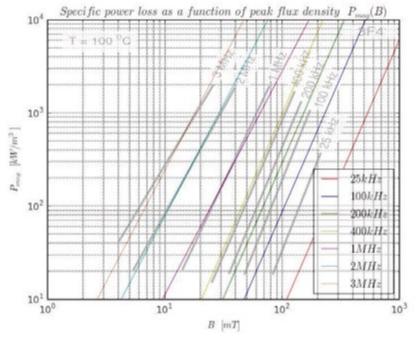

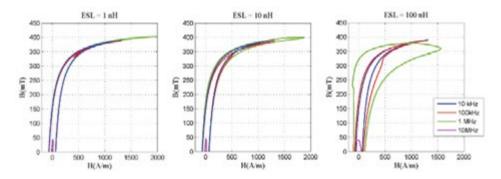

Soft magnetic materials studied for the design of miniaturized power inductors and transformers present loss mechanisms related to magnetic hysteresis loop area which overall accounts for the quasi-static hysteresis and frequency-dependent eddy currents [2]. The estimation of magnetic material's losses depends much on the operating conditions of the core (i.e. applied current waveform shape, amplitude and frequency [20, 21], DC bias [22, 23], and temperature [24]) so it is important to characterize the hysteresis by investigation of these experimental parameters. Due to the high frequency of operation, new models and measurement techniques need to be developed, to characterize the magnetic materials of interest. Once these materials are correctly characterized their behavior in terms of inductance and power losses can be modeled, to find the optimal solution depending on the constraints set by the power conversion task required.

#### 1.3.2 Capacitors

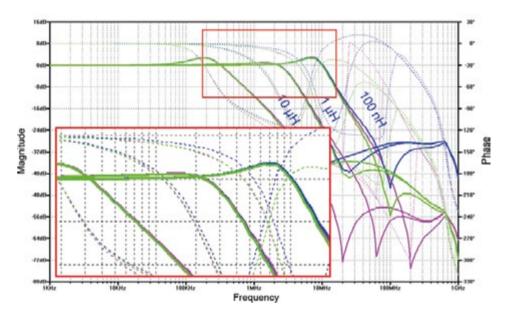

With respect to capacitors, the technology for the realization of miniaturized components working in a range up to 100 MHz and even more is already available. This development has been achieved under the drive of applications in digital electronics and RF telecommunications which require very stable capacitances capable of working at high frequency with low parasitic series inductance (ESL) and low parasitic series resistance (ESR). Ceramics are actually the most relevant dielectric material in these applications. In fact, due to the advent of new materials and multi-

layer ceramic capacitors (MLCC), in 1980's capacitors were a main drive to move from through-hole to SMD mounting techniques.

Today it is possible to recognize two different classes of ceramic capacitors, depending on their dielectric material. Class I is based on dielectrics realized with a fine granular mixture of paraelectric materials, like titanium dioxide  $TiO_2$ , which is additivated with zinc, zirconium, niobium, magnesium, tantalum, cobalt and strontium, to improve the linearity of its characteristics [25]. This class offers the most stable capacitances while it has the lowest capacitance density. Ceramics belonging to this class are the NP0, CG and C0G for example. Class II ceramics are based on materials like barium titanate BaTiO<sub>3</sub> and suitable additives are aluminum silicate, magnesium silicate and aluminum oxide. These dielectrics have much higher permittivity than class I and therefore they have a better capacitance density. However, their permittivity is dependent on the applied field so they have capacitance values which are highly non-linear with temperature and voltage. Common materials of this class are X7R, Y5V, Z5U. Nowadays, MLCC SMD capacitors in size 1210 are available with capacitance values up to 220  $\mu F$  and  $V_{Max} = 6.3 V^{I}$  and, over the last few years, they already became a valid alternative to electrolytic and tantalum capacitors in applications as low voltage power supply decoupling.

However, referring to the miniaturization of power supplies, a gap in terms of capacitance density between SMD capacitors and integrated capacitors on silicon like CMOS or metal-insulator-metal (MIM) capacitors is still existing. Some PwrSiP have adopted solutions which used co-packaged SMD capacitors to provide the required decoupling to the converter, due to the fact that it is still very hard to achieve good capacitance density and low ESR and ESL for integrated capacitors without consuming much silicon area.

A promising technology is the passive integrated connective substrate (PICS) proposed by Ipdia [26, 27]. Matrices of deep pores realized on the Si surface with dry etching are used to maximize the capacitance density over area. The bottom electrode is realized with  $n^+$  doped Si, the dielectric is a deposited layer and the top electrode is a layer of  $n^+$  poly-silicon. The company claims a capacitance density up to  $2 \mu F/mm^3$ , ultra-low ESL performances which overperforms by more than 15 dB an X7R ceramic capacitor in terms of frequency rejection [27] and very stable temperature behavior. However, even if these capacitors are realized on a Si substrate, they are realized on a separate die with respect to the rest of electronics. Moreover, even if it could be possible to consider a simultaneous fabrication with electronics on the same die, the vertical trench process required for their fabrication does not allow to place part of the circuitry under them.

Finally, as a general consideration, dielectric materials, as magnetic ones, are also limited due to their frequency dependent behavior. The dielectric constant is often modeled as a complex quantity which changes with frequency providing both

<sup>&</sup>lt;sup>1</sup> March, 2015 [Online]: www.digikey.com

<sup>&</sup>lt;sup>2</sup> March, 2015 [Online]: http://www.ipdia.com/index.php?page=our\_products&cat\_id=2

capacitance and resistive parasitic components. A higher switching frequency leads to increased losses and reduced capacitance value. In order to achieve higher frequency operation with higher efficiencies, better materials are required to reduce capacitor dissipation factor by 1/3 to 1/10 and increase capacitor energy and power densities 2 to 10 times those available today [5].

#### 1.4 Converter topologies

Depending on the application, conventional converter topologies can provide significant limitations while moving towards higher switching frequencies and miniaturization. These limitations are related to switching and conduction losses or to the specific constraints imposed by switches and passive devices in terms of efficient behavior, maximum voltage and maximum current limitations.

For these reasons, a specific attention should be payed to converter circuital architectures, topologies and control techniques in order to develop solutions which minimizes the limitations previously mentioned. By circuital architectures it is intended the possibility of connecting several DC-DC converters of the same type or of different types in parallel or stacked in order to provide a single power conversion functionality while exploiting benefits like voltage or current sharing among the different sections. The most common example is the multiphase connection of buck converters where two or more buck converters are connected in parallel and switched with a phase difference such that their inductor currents are interleaved [28]. This allows to broaden the current load range while minimizing output current and voltage ripples due to interleaving. Parallel connections of different converters is generally used to enlarge the load range of converters with efficient behavior of the single unit limited to narrow loads [29]. In these cases, additional considerations related to the control of the different phases comes into play [30]. Other architectures are exploiting stacked connections of converter topologies in order to deal with higher input voltages in a modular way [31]. With respect to the circuital topologies of the converters and also their control techniques, a classification can be done depending on the switching frequency of the converter, where two main ranges are generically identified.

#### 1.4.1 High frequency power conversion

Converters working in the range *1* to *30 MHz* are considered part of the high frequency (HF) power conversion. Generally speaking, these converters are usually requiring magnetic core inductors in order to achieve significant inductance density in the considered frequency range. They are usually based on Si devices and the frequency range allows a very good freedom in terms of circuital topology solutions. This freedom is mostly related to the capability of using CMOS and LDMOS devices in silicon processes for the realization of converters working with this frequency range. This allows the possibility of realizing power switches and auxiliary electronics (i.e. gate drivers, logic, error amplifiers, etc...) directly on the same silicon die greatly increasing the power density. The circuital topologies used for HF

power conversion exploits various techniques to overcome the limitations associated with power switches voltage and current ratings. Starting from the previously mentioned techniques of ZVS and ZCS, which are applied even to conventional topologies, there is strong drive towards a wide collection of new topologies aiming at solving specific limitations and, optionally, using also ZVS/ZCS. For example, voltage stacking or cascoding is adopted by connecting multiple power switches in series in order to block higher voltages using series of low voltage-rated devices which can have better  $R_{dson}Q_g$  figure of merit and in general lower parasitics. Moreover, topologies made of multiple conversion stages are used to obtain a pre-regulation working at a lower frequency and a load regulation switching at higher frequency with a lower voltage swing on inductors and switches and thus reduced losses. In this direction, new topologies aiming at single-stage behavior, like the "High stepdown multiphase buck", which will be treated in Chapter 2, or the "Multi-level converters" [32] results in favorable trade-offs in terms of decreasing the switching ripples, reducing the size of the filter elements, increasing the converter open-loop bandwidth, or increasing the converter efficiency.

In this frequency range, ordinary control techniques, based voltage mode or current mode controls [2] are being challenged by mixed signal control techniques. These techniques exploits digital acquisition of the output voltage to adopt a non linear control during load transients optimized to provide the minimum voltage deviation of the output [33]. This allows to reduce the current stress on components and a reduction of output passive components' sizes which can be based only on the physical limitation of the converter or even on the ripple requirements only.

#### 1.4.2 Very high frequency power conversion

Above 30 MHz, converters are considered part of the very high frequency (VHF) power conversion. In this frequency range, it is possible to design converters working with reduced inductance values such that air core inductors can be a main alternative in design. However, to achieve such dramatic increases in switching frequency while preserving a reasonable efficiency, it is necessary to counter the frequency dependent device loss mechanisms such as switching and gating losses. For this reason, these converters are usually implementing resonant ZVS/ZCS operation. Due to the need of limiting the gating losses and to the difficulty of implementing an high side gate driver at such high frequencies, this topologies are often based on a single ground referenced switch and the most commonly evaluated topologies are directly inspired to the Class-E power amplifier [34] although there are exceptions to this approach [35].

The principle of operation of Class-E based approach exploits the resonance between two or more passive components, usually an input choke inductor and a capacitor connected in parallel with the switch, to achieve zero voltage switching and zero current switching, by allowing switch turn-on when both its  $V_{ds}$  and  $dV_{ds}/dt$  are zero. Moreover, semiconductor device's parasitics (i.e. interconnection inductance and device capacitances) must be absorbed in this resonant circuit operation. The resonant operation requires switches rated for voltages much higher than the input voltage (i.e. around 2 to 3 times), due to the over-voltage generated by the resonant

behavior and in general the components' stress is higher than in hard switched topologies. In order to reduce this requirement, other topologies like the Class  $\Phi_2$  converter have been developed [36]. This topology use a multi-resonance operation (by adding an inductor and a capacitor) to reshape the switching node voltage waveform such that it has a lower maximum (i.e. a switch with a lower voltage rating can be used) and also reduces the sensitivity of ZVS on load.

In fact, VHF converters, due their resonant behavior, which is highly dependent on load impedance, tend to suffer from poor efficiency outside of nominal load operation. Circuital modifications or control techniques aiming at their efficient load range extension and regulation have been evaluated. A possible solution is by using an architecture composed by several parallel converters controlled with an on/off management depending on the load [29].

#### 1.5 Thesis structure and contribution

Following the previous introduction, this thesis aims at the study and design of topologies and components for high power density DC-DC converters. It is clear that new circuital topologies can solve specific problems which arise when moving to higher switching frequencies. In order to leverage a possible integrated realization of the converter's active components on a single die we decided to focus on the use of available Si process technologies for our designs. These allow to use well established and reliable technologies sharing on the same die CMOS devices, which could be used to implement the auxiliary logic and analog circuitry, together with power devices such as lateral diffusion mosfets (LDMOS) and drain extended (DEMOS) power transistors which can be used to implement the converter's power stage.

This choice has led to the study and design of a novel integrated implementation of a four phases high step-down multiphase buck converter, which is presented in Chapter 2. At first, the performance comparison with a multiphase buck topology is recalled from previous literature contributions and expanded. This comparison underlines the benefits of the high step-down topology when moving to high step-down conversion from input to output voltage and at the same time moving to higher frequencies for power density enhancements. The main circuital design considerations and optimizations related to its integrated implementation are described. Measurement results are presented and compared against previous solutions in terms of achieved power density.

Still, considering high step-down topologies, but using indirect charge transfer, a preliminary study for a high power density stackable flyback architecture is presented in Chapter 3. As for the high step-down multiphase buck, the aim is to enhance the power density of the actual discrete components version of the converter moving to a modular architecture based on modules implementing an integrated flyback converter with co-packaged miniaturized transformer. The study has been focused on the study of literature on HF flyback converters and on the optimization of a micro-transformer which could be implemented as flyback inductor. Additional considerations have been focused on the implementation of primary side flyback

Study and design of topologies and components for high power density DC-DC converters

switch with commercially available discrete switches aiming at the development of a test-bench for the preliminary evaluation of transformer performances.

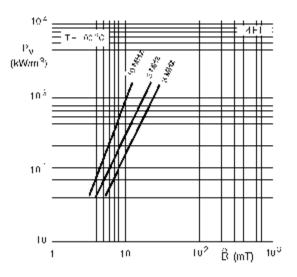

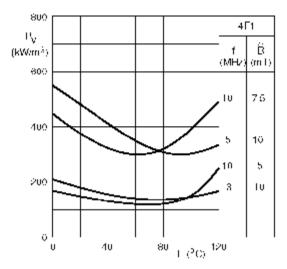

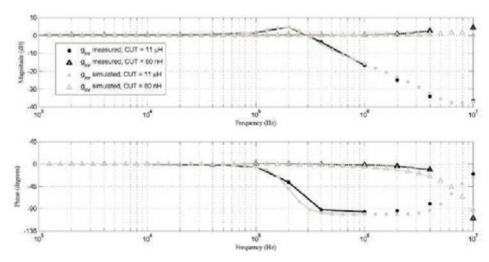

Due to the fact that HF converters are much dependent on magnetic core inductors performances, we have found of interest the modeling of magnetic core losses in order to improve the capability of optimizing the design of miniaturized magnetic core inductors. Chapter 4 reviews the losses contributions in magnetic core power inductors, considering their dependencies on operating conditions. Various core losses models are considered in order to obtain the most versatile model in terms of power inductors' typical current and voltage waveforms. A magnetic hysteresis model is described and its simulated results are compared against magnetic material hysteresis and losses behaviours obtained from datasheets.

As the modeling of magnetic hysteresis and its related losses requires quite a significant number of parameters and characterization, the design of an automated electronic system capable of hysteresis characterization on physical samples of magnetic materials used for HF power conversion is described in Chapter 5. Different measurements depending on frequency, temperature and magnetic field waveform are obtained focusing on the future idea of using them for modeling calibration.

Fig. 1.1. Buck converter topology and related waveforms.

Fig. 1.2. Impact of increase in switching frequency on the relative value of passive elements for a buck converter [1].

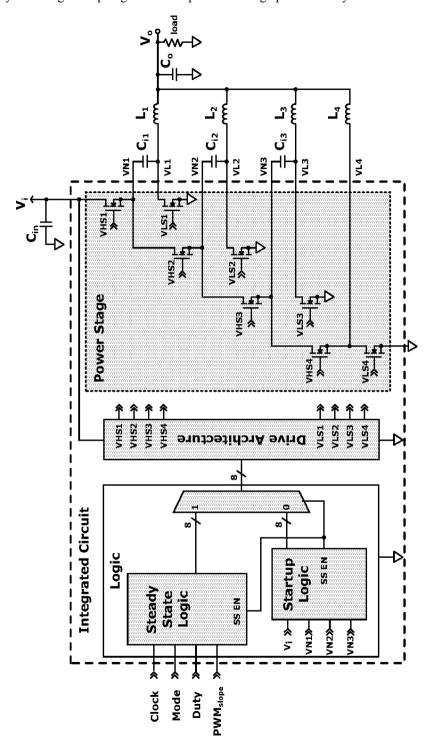

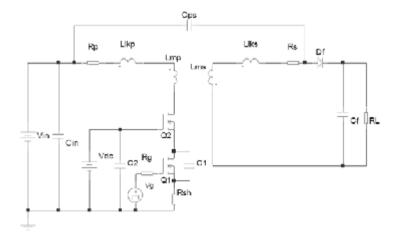

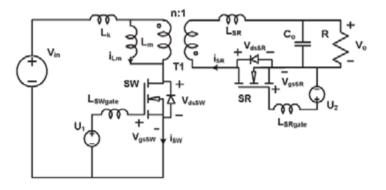

## Chapter 2 Integrated high step-down multiphase buck design

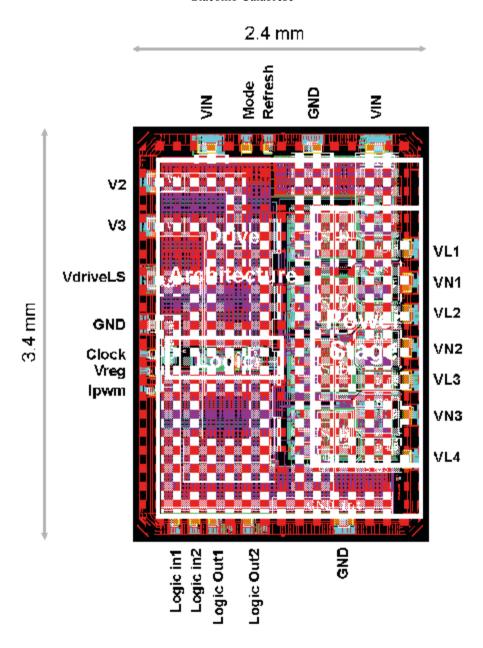

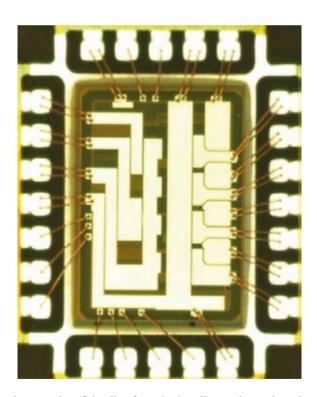

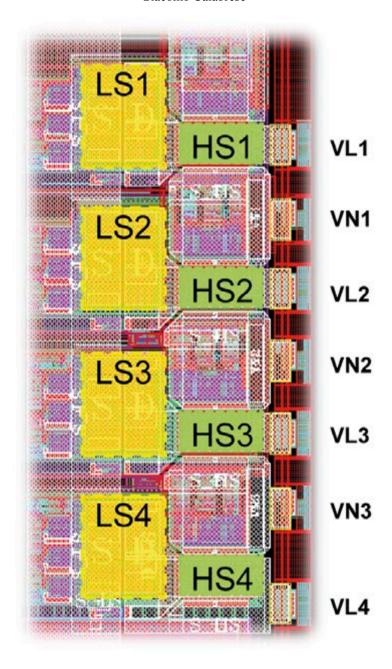

This chapter presents the design of an integrated high step-down multiphase buck converter. The design exploits the integration on a single die of a four phases high step-down power stage and drive architecture to obtain a switching frequency increase from the range of [500 kHz, 1 MHz] of previously proposed solutions to a value of 10 MHz. This provides a dramatic reduction of external passive components values and a relative increase in terms of output power density estimated taking into account the area of the converter. Moreover, the frequency increment can provide benefits in terms of dynamic behavior and output ripple reduction. In order to clarify this assumptions, the principle of operation of the high step-down multiphase buck is reviewed and the principal advantages with respect to a multiphase buck are underlined. The integrated realization allows to optimize the sizing of the power switches and to design a custom drive architecture. It also relieves the implementation burden associated with complex circuitry by minimizing parasitics related to interconnections. This advantage has been applied to design the auxiliary blocks required. Among them, a proper start-up sequence for this topology has been designed. Different values and types of commercial power inductors have been tested showing a trade-off between best power density and best efficiency.

#### 2.1 Introduction

CPUs of actual PCs and laptops have supply voltages in the range 0.9-1.5 V and require up to several tens of Amperes when computing at full speed. They behave as highly dynamic loads with slew rates up to hundreds of  $A/\mu s$  when the CPU switches from being idle to full processing. They are usually supplied by a point-of-load Voltage Regulator (VR) which directly converts power from the main power supply or battery (e.g. laptops), which provide voltages in 12-19 V range. The VR should not only be capable of working efficiently with a high step-down voltage conversion ratio, it should also provide the CPU the required current with an adequate dynamic response.

A widely adopted topology for this kind of VRs is the synchronous multiphase buck converter. This topology can provide quite large output currents, due to the multiphase architecture, and an output ripple reduction due to interleaved phase switching [37, 38]. Moreover, using switching frequencies up to hundreds of kHz per each of the *n* phases, a proper interleaving provides an equivalent output switch-

ing frequency n times greater thus improving the transient response and reducing the output ripple. However, VRs based on multiphase bucks present some main issues. First of all, the high step-down voltage conversion requires the buck topology to work with very small duty cycles, around 10% (i.e. 1.2 V out with 12 V input) or lower. This causes a reduced range for duty, and thus output, regulation and ultimately limits the possibility of increasing the switching frequency. In fact, as the required on time of the high side switch becomes comparable with the driver rise time, duty cannot be controlled. Another issue related to the buck topology is that each switch must be rated to block the input voltage. This causes that the switches turn-on and turn-off power losses are directly proportional to the input voltage. Moreover, due to their voltage rating, the switches will usually have a worse figure of merit (FOM) than switches rated for lower voltages (e.g. higher  $R_{dson}$   $Q_g$ ). An additional drawback of a multiphase buck topology is related to the necessity of a current sensing technique monitoring the current balance between different phases.

In order to solve these issues, especially the limited duty cycle, two different methods have been evaluated in literature. The first one is based on a two-stage architecture where a pre-regulator stage provides a step-down conversion of the input voltage before applying it to the multiphase buck [39]. However, this method needs the introduction of many additional components, with respect to a multiphase buck, increasing the overall cost of the converter. The second method is based on maintaining a single-stage converter, trying to extend the duty cycle by means of transformers or coupled inductors [40, 41, 42]. These solutions have less additional components but are limited by the performances of the magnetics. Moreover, it is often required the design of custom magnetics, instead of using commercially available ones, increasing the cost and design time of the overall converter.

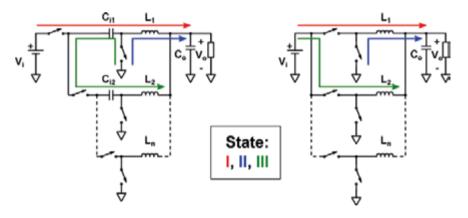

Another solution, which follows from the second method, is based on obtaining the duty cycle extension modifying the multiphase buck topology and adding capacitors instead of inductors. This solution which is referred to as "Extended-Duty Multiphase Buck" has been extensively described in [43]. A comparison with multiphase buck has been evaluated in [44] and additional characterizations of this solution for a different number of phases have been studied in [45, 46, 47] where the topology is referred as "High Step-Down Multiphase Buck". The high step-down multiphase buck topology provides advantages, with respect to the multiphase buck topology, not only in terms of duty cycle extension but also in terms of voltage stress of the switches and automatic current balance between the different phases [45].

A reduced voltage stress of the switches, allows to use switches rated for a lower voltage. These usually have smaller parasitic capacitances and consequently can be switched faster. Moreover, their reduced voltage stress allows to reduce the switching losses of the converter. These advantages allows to increment the switching frequency of the converter which allows to decrease the size of inductors and capacitors while mitigating the increment of switching losses. In order to understand the advantages in the comparison between high step-down multiphase buck converter and standard multiphase buck converter, the operation principle of high step-down multiphase buck is recalled in section 2.2.

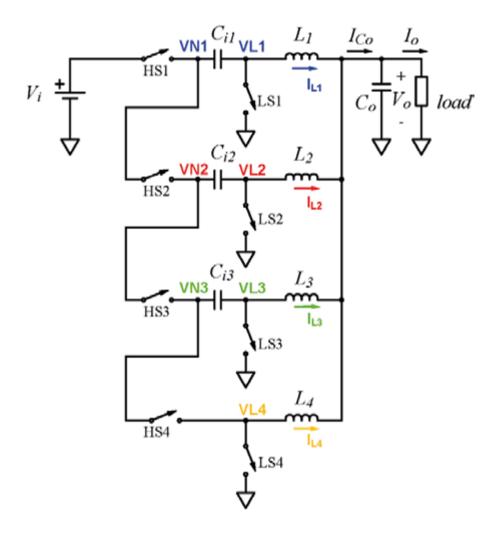

#### 2.2 High step-down multiphase buck operation analysis

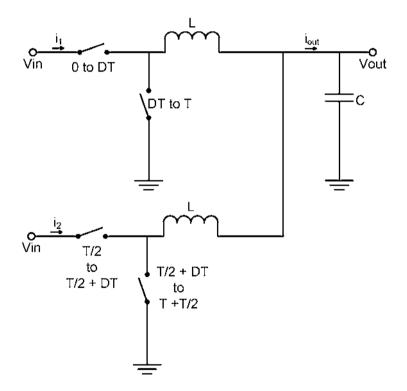

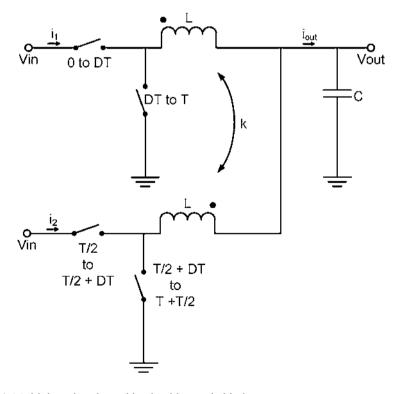

We will directly focus on the analysis of a four phases converter in order to have convenient notation and graphs which can be used throughout the rest of the chapter. Fig. 2.1 shows an ideal four phases high step-down buck topology. Different colors have been associated with signals related to each phase to allow an easier identification of the four phases. HSx labels identify the high side switches while LSx low side ones with x as the phase number. Between each phase's HS and LS switch, there are three intermediate flying capacitors  $C_{i1}$ ,  $C_{i2}$  and  $C_{i3}$ , exception made for phase number 4. For this reason, two switching nodes can be defined for the first three phases. The upper nodes of each flying capacitor are named VNx and the lower nodes, which correspond to the nodes connected to the inductor, are named VLx. As it is possible to notice, only the first phase's input is directly connected to the input voltage  $V_i$ . Other phases' inputs are connected to VNx node of phase x-I, in a kind of cascaded structure. With respect to the outputs, the inductors are connected in parallel as it happens in a standard multiphase buck to obtain a sum of their output currents with switching phase interleaving.

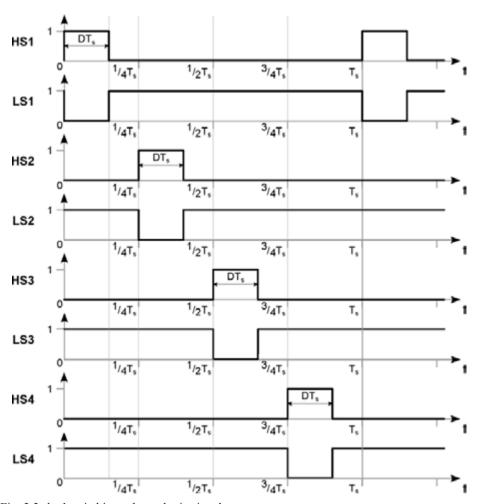

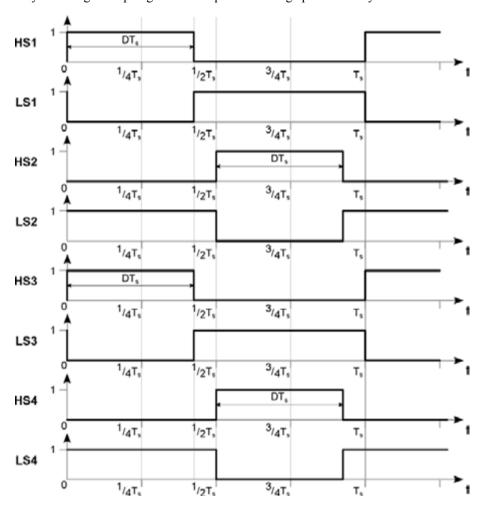

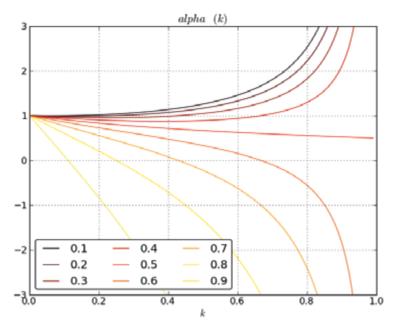

With four phases there are two possible switching schemes which can used for interleaving. In order to easily identify them, we can start by defining k as the number of non-adjacent High Side (HS) switches simultaneously turned on. Depending on which scheme is selected, we can have k = 1, 2. With k = 1 we have a sequential switching of the four HS switches in a pattern 0-90°-180°-270° of phase shift between each HS logic signal. The second scheme, with k = 2, has a pattern which involves a switching of 2-by-2 non-adjacent HS switches in a pattern 0-180°-0-180°. A correct disoverlap must be respected between each phase HS and Low Side (LS) switches turn-ons and also between adjacent HS. The two switching schemes are analyzed in the following sections. For simplicity we will assume that each phase has the same duty cycle D.

#### 2.2.1 Sequential high side switches turn-on: k=1 switching scheme

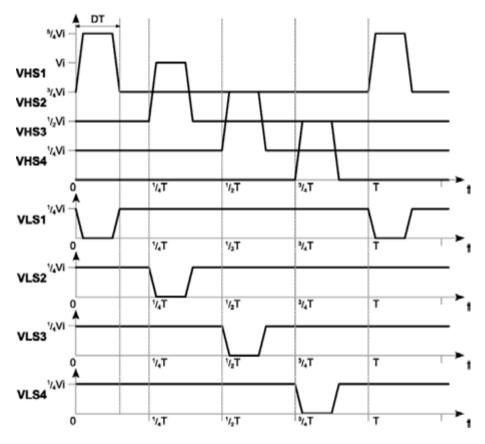

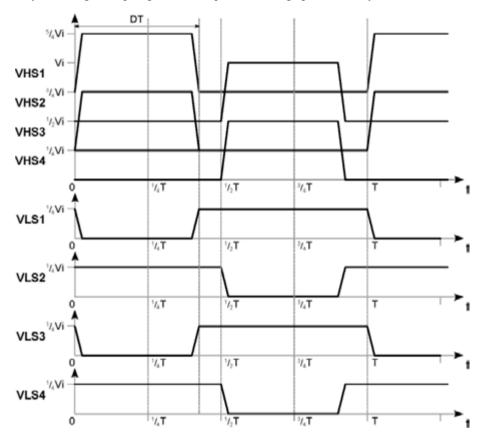

The k = 1 switching scheme has only one HS switch turned on at a time. The logic signals necessary to control the switches in order to obtain this pattern are shown in Fig. 2.2.

As it is possible to notice, in order to keep this switching scheme, there is a constraint on maximum duty cycle:

$$D < \frac{1}{4}.\tag{2.1}$$

In order to calculate the voltage conversion ratio, we can proceed with the steady-state analysis of the converter. In order to simplify equations, we will define the voltages across flying capacitors as:

$$V_{Ci1} = VN1 - VL1; (2.2)$$

Study and design of topologies and components for high power density DC-DC converters

$$V_{Ci2} = VN2 - VL2; (2.3)$$

$$V_{Ci3} = VN3 - VL3. (2.4)$$

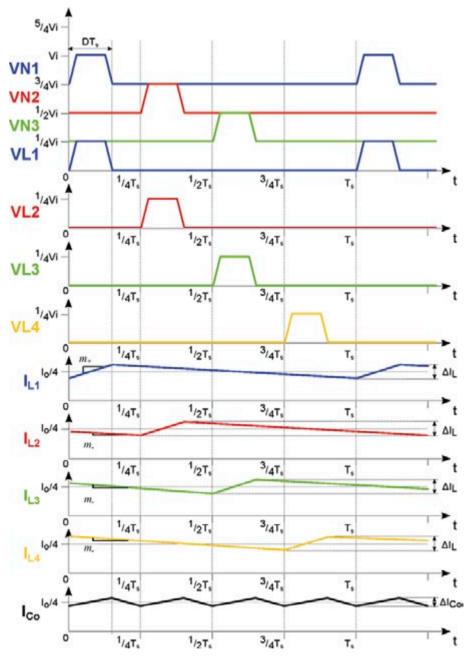

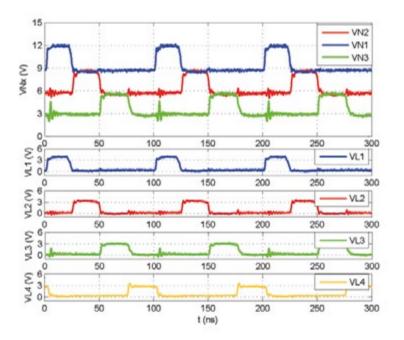

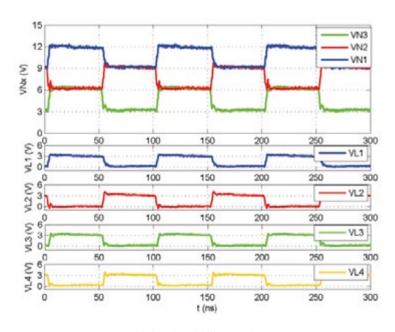

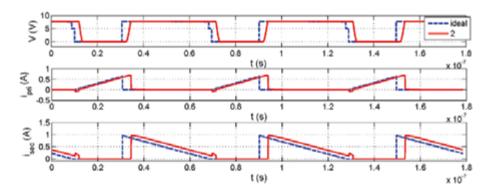

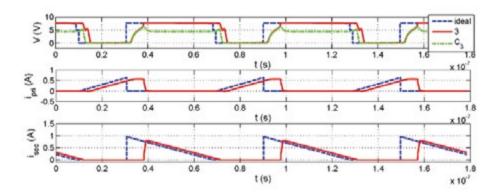

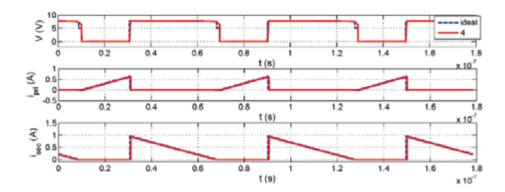

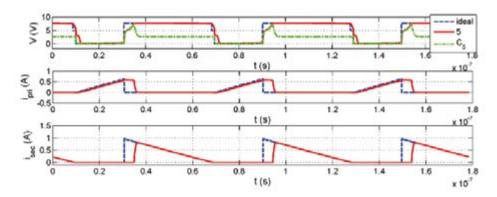

The steady state waveforms of each of the switching nodes and currents are shown in Fig. 2.3.

There are eight different states during each switching period  $T_s$ . Instead of analyzing each different state, it is easier to analyze phase 1 over the whole period and apply similar considerations for the other phases.

HS1 is turned on for a time DT. During this phase  $L_I$  is charged through  $C_{iI}$  with an applied voltage difference  $V_{LI^+} = V_i - V_{CiI} - V_o$ . Thus the current  $I_{LI}$  rises of a quantity:

$$\Delta I_{L1+} = \frac{V_i - V_{Ci1} - V_o}{L_1} DT_s,\tag{2.5}$$

with slope  $m_{I+}$ :

$$m_{1+} = \frac{V_i - V_{Ci1} - V_o}{L_1}. (2.6)$$

LS1 is on for a time (I-D)T.  $L_I$  is discharged on the output with an applied voltage difference  $V_{LI} = -V_o$ . The current  $I_{LI}$  decreases of a quantity:

$$\Delta I_{L1-} = -\frac{V_o}{L_1} (1 - D) T_s, \tag{2.7}$$

with slope  $m_{1}$ :

$$m_{1-} = -\frac{V_o}{L_1}. (2.8)$$

By the assumption of steady state operation we have that inductor volt-second balance is constant, thus:

$$\Delta I_{L1+} = |\Delta I_{L1-}|,\tag{2.9}$$

which gives:

$$(V_i - V_{Ci1} - V_o)D = V_o(1 - D). (2.10)$$

With respect to phase 2 we have a similar analysis, except for the fact that when HS2 is on we have a voltage difference on  $L_2$  which is  $V_{L2+} = V_{Ci1} - V_{Ci2} - V_o$ . Consequently:

$$\Delta I_{L2+} = \frac{V_{Ci1} - V_{Ci2} - V_o}{L_2} DT_s \tag{2.11}$$

$$\Delta I_{L2-} = -\frac{V_o}{L_2} (1 - D) T_s. \tag{2.12}$$

For phase 2 from volt-second balance we obtain:

$$(V_{Ci1} - V_{Ci2} - V_o)D = V_o(1 - D). (2.13)$$

Phase 3 gives:

$$\Delta I_{L3+} = \frac{V_{Ci2} - V_{Ci3} - V_o}{L_3} DT_s \tag{2.14}$$

$$\Delta I_{L3-} = -\frac{V_o}{L_3} (1 - D) T_s. \tag{2.15}$$

And its volt-second balance relation is:

$$(V_{Ci2} - V_{Ci3} - V_o)D = V_o(1 - D). (2.16)$$

Phase 4 gives:

$$\Delta I_{L4+} = \frac{V_{Ci3} - V_o}{L_4} DT_s \tag{2.17}$$

$$\Delta I_{L4-} = -\frac{V_o}{L_4} (1 - D) T_s. \tag{2.18}$$

Which provides the last volt-second balance equation:

$$(V_{Ci3} - V_o)D = V_o(1 - D). (2.19)$$

Combining equations 2.10, 2.13, 2.16, 2.19 we have the set:

$$\begin{cases} (V_i - V_{Ci1} - V_o)D = V_o(1 - D) \\ (V_{Ci1} - V_{Ci2} - V_o)D = V_o(1 - D) \\ (V_{Ci2} - V_{Ci3} - V_o)D = V_o(1 - D) \\ (V_{Ci3} - V_o)D = V_o(1 - D) \end{cases}$$

(2.20)

Study and design of topologies and components for high power density DC-DC converters which can be simplified as:

$$\begin{cases} (V_{i} - V_{Ci1})D = V_{o} \\ (V_{Ci1} - V_{Ci2})D = V_{o} \\ (V_{Ci2} - V_{Ci3})D = V_{o} \\ V_{Ci3}D = V_{o} \end{cases}$$

(2.21)

and is easily solvable, giving:

$$V_{Ci1} = \frac{3}{4}V_i; (2.22)$$

$$V_{Ci2} = \frac{2}{4}V_i; (2.23)$$

$$V_{Ci3} = \frac{1}{4}V_i. {(2.24)}$$

At steady state the flying capacitors are charged at a constant voltage which are fractions of  $V_i$  proportional to the number of phases. It also follows that the conversion ratio of the converter is:

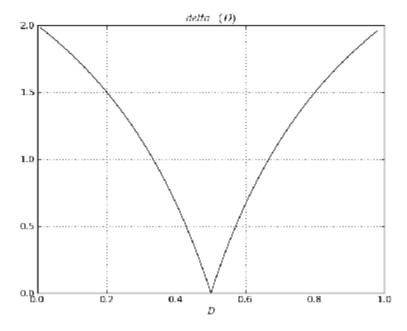

$$\frac{V_o}{V_i} = \frac{D}{4} \quad with \quad D < \frac{1}{4}.$$

(2.25)

It is interesting to notice that, as for the conventional buck operated in CCM, the conversion ratios are completely independent from the values of the inductors. Additionally to that, also the capacitors' voltages remain independent from inductors' values. However, inductance values influence the current ripples, which depend on inductance value at their denominator. For simplicity we assume that inductors are all equal thus  $L_1 = L_2 = L_3 = L_4 = L$ . The positive and negative slopes  $m_{+x}$  and  $m_{-x}$  (with x = 1, 2, 3, 4) of the inductors' currents become all equal among the phases and can be rewritten in the form:

$$m_{+} = \frac{\frac{V_{i}}{4} - V_{o}}{L},\tag{2.26}$$

$$m_{-} = -\frac{V_o}{L}. (2.27)$$

From this follows that the inductors' current ripples are all equal to:

$$\Delta I_L = \frac{V_o}{I} (1 - D) T_s. \tag{2.28}$$

In order to compare with a multiphase buck we should express D as expressed by equation 2.25 which gives:

$$\Delta I_L = \frac{V_o}{L} \left( 1 - 4 \frac{V_o}{V_i} \right) T_s. \tag{2.29}$$

For a multiphase buck we have that  $D = V_o/V_i$  so inductor's current ripple is:

$$\Delta I_{Lmb} = \frac{V_o}{L} \left( 1 - \frac{V_o}{V_i} \right) T_s. \tag{2.30}$$

This shows how there is a ripple reduction on each phase with respect to the multiphase buck.

If we consider the output current going to the capacitor  $I_{Co}$ , this will be:

$$I_{C_0} = I_{L1} + I_{L2} + I_{L3} + I_{L4}. (2.31)$$

Its ripple is the output capacitor ripple  $\Delta I_{Co}$  while the DC value is the current flowing to the load  $I_o$ . The capacitor current ripple can be evaluated by considering that, at steady state, it will have a period of  $T_s/4$ . From Fig. 2.3 it is easy to notice that with  $DT_s \le t < T_s/4$  the currents on the four phases have the same slope  $m_-$ , thus:

$$\Delta I_{Co} = 4|m_{-}|\left(\frac{1}{4} - D\right)T_{s} = \frac{V_{o}}{L}(1 - 4D)T_{s}.$$

(2.32)

Still considering the substitution of D we have:

$$\Delta I_{Co} = \frac{V_o}{L} \left( 1 - 16 \frac{V_o}{V_i} \right) T_s. \tag{2.33}$$

While a four phases multiphase buck with the same interleaving would have:

$$\Delta I_{Co\ mb} = \frac{V_o}{L} \left( 1 - 4 \frac{V_o}{V_c} \right) T_s. \tag{2.34}$$

The k=1 switching scheme provides a very high step-down from input to output. The duty cycle of the switches is extended with respect to the standard multiphase buck by a factor of four. However this imposes a limit on the maximum output voltage which is obtained for  $D_{max} = 1/4$  and is:

$$V_{o max} = \frac{V_i}{16}. (2.35)$$

With  $V_i = [10, 16] V$ , it provides  $V_{o max} = [0.625, 1] V$  which is quite low for actual power supply values. For this reason k = 2 has been analyzed, too.

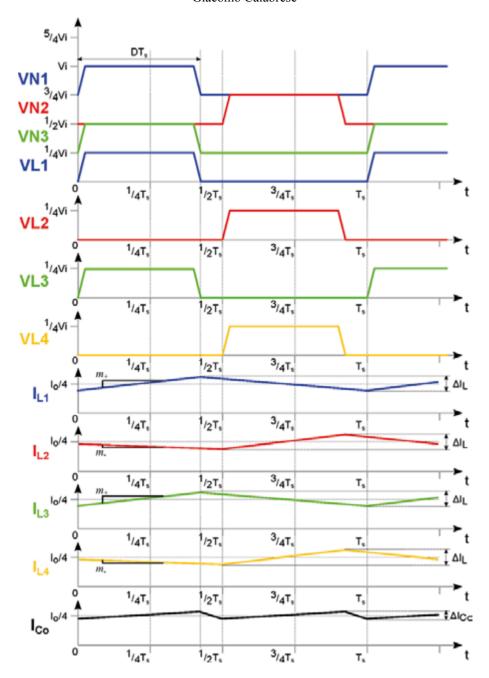

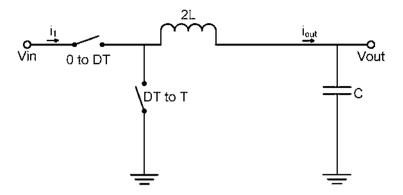

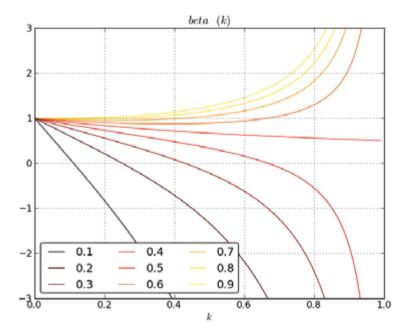

#### 2.2.2 Two-by-two high side switches turn-on: k=2 switching scheme

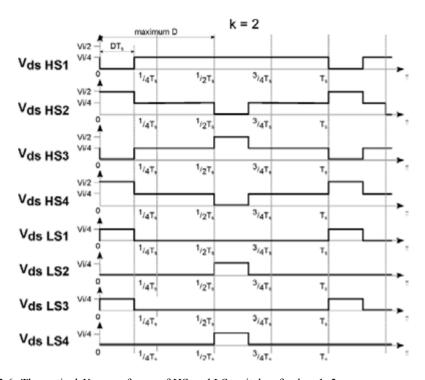

This scheme provides an additional duty cycle extension with respect to standard multiphase buck and also with respect to the k = 1 switching scheme. In this case the HS switches are turned on in couples, HS1 and HS3 together, then the other two. Fig. 2.4 shows the required logic signals.

In this case, the constraint on the duty is relaxed to:

$$D < \frac{1}{2}.\tag{2.36}$$

The steady state waveforms of each of the switching nodes and currents are shown in Fig. 2.5.

Following a steady state analysis similar to the one treated in subsection 2.2.1 it is possible to obtain the same flying capacitors' voltages of equations 2.22, 2.23, 2.24 also for this switching scheme. The conversion ratio is the same, but with the relaxed constraint on duty:

$$\frac{V_o}{V_i} = \frac{D}{4}$$

with  $D < \frac{1}{2}$ . (2.37)

Under the same assumptions, we obtain  $m_+$  and  $m_-$  equal to the k=1 analysis. The current ripples on each inductor are still equal to equation 2.29. However, with respect to the output capacitor ripple there are some differences related to the different interleaving of the currents.

Considering the interval of  $I_{Co}$  in Fig. 2.5, with  $DT_s \le t < T_s/2$  all the inductor currents are assuming a negative slope, thus:

$$\Delta I_{Co} = 4|m_{-}|\left(\frac{1}{2} - D\right)T_{s} = \frac{V_{o}}{L}(2 - 4D)T_{s}. \tag{2.38}$$

Which, with the substitution of *D* comes out to be:

$$\Delta I_{Co} = \frac{V_o}{L} \left( 2 - 16 \frac{V_o}{V_i} \right) T_s. \tag{2.39}$$

A multiphase buck with same interleaving would have:

$$\Delta I_{Co\ mb} = \frac{V_o}{L} \left( 2 - 4 \frac{V_o}{V_i} \right) T_s. \tag{2.40}$$

So there is still a reduction of the capacitor ripple, but less than for the k = 1 case. Nevertheless, this time the maximum output voltage is:

$$V_{o max} = \frac{V_i}{8} \tag{2.41}$$

giving  $V_{o max} = [1.25, 2] V$  with  $V_i = [10, 16] V$ .

This switching scheme sacrifices part of the ripple reduction in order to obtain an additional duty cycle extension and higher  $V_{o\ max}$  which can be more useful in practical applications.

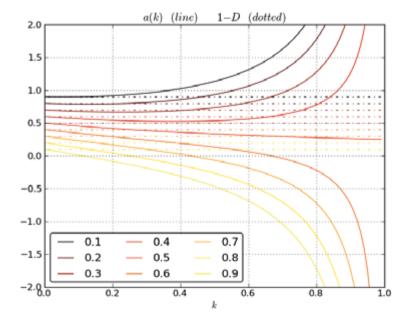

#### 2.3 Comparison with multiphase buck

Different characteristics need to be evaluated in order to define a comparison between high step-down multiphase buck and standard multiphase buck. These different aspects have already been presented in the cited literature describing discrete implementations of the high step-down topology. Table 2.1 collects these aspects considering also the two possible switching schemes. Due to the similarity of these topologies with the single phase buck architecture, we will report the same parameters evaluated also for the buck. This gives an easily understandable comparison with a widely known topology. Each parameter is presented considering a generic number n of phases.

The conversion ratio  $V_o/V_i$  proves the duty cycle extension between the high step-down topology and the standard buck topologies. This advantage, as we already introduced, is mostly based on the reduced voltage swing of the inductors.

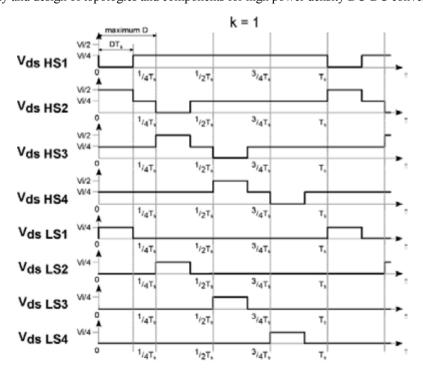

Additionally, this provides a reduced blocking voltage of the switches, reported in Table 2.1 as  $V_{ds\ max}$ . Both HS and LS switches are blocking reduced voltages with respect to the single and multiphase buck's switches. The  $V_{ds\ max}$  of each switch can be obtained from Fig. 2.3 and Fig. 2.5 considering the differential voltages on each switch. The resulting waveforms are shown in Fig.2.6. As it is possible to notice, even if the HS switches have  $V_{ds\ max} = V_1/2$ , each switch is turned on and off on a  $V_{ds\ on/off} = V_1/4$ . This allows to reduce the switching losses with the high step-down topology.

The reduced inductor's voltage swing provides also a reduction of inductor's current ripple  $\Delta I_L$  with the high step-down topology. A smaller inductance value, thus a smaller inductor, can be used in order to obtain the same requirement on ripple or the same inductor can be used with a lower current ripple, providing reduced core losses.

An additional benefit of inductor ripple reduction can be seen on output capacitor ripple  $\Delta I_{Co}$ . In this case, also the multiphase buck can provide an advantage on the single phase buck due to phase interleaving. Nevertheless, the high step-down topology provides an even increased ripple reduction. This reduction, as we already demonstrated above, is maximized with k=I switching scheme. A reduction of the output capacitor's current ripple allows to obtain an output voltage ripple inside the requirements using a smaller capacitance value which often implies using a smaller sized capacitor.

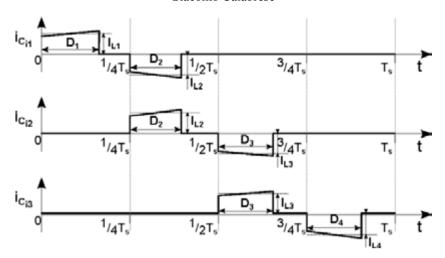

An interesting advantage of the high step-down topology is related to the automatic balance of the inductors' currents. This is directly related to the presence of the capacitors  $C_{ix}$ . Fig. 2.7 shows the three  $C_{ix}$  capacitors' currents over a switching period. Assuming different duty cycles for each of the phases, the steady state charge balance of  $C_{ix}$  capacitors over a switching period must be zero. Thus:

Study and design of topologies and components for high power density DC-DC converters

$$Q_{1\,ava} = (D_1 I_{L1} - D_2 I_{L2}) T_s = 0 (2.42)$$

$$Q_{2\,ava} = (D_2 I_{L2} - D_3 I_{L3}) T_s = 0 (2.43)$$

$$Q_{3 ava} = (D_3 I_{L3} - D_4 I_{L4}) T_s = 0 (2.44)$$

These equations can be combined to obtain the relation shown in Table 2.1:

$$I_{L1}D_1 = I_{L2}D_2 = I_{L3}D_3 = I_{L4}D_4. (2.45)$$

This means that the imbalance of currents is almost removed without any additional sensing requirements. To the extent that each phase is controlled with the same duty cycle, the four currents are equal.

The inductor's current maximum slew rate, max  $di_L/dt$ , is a parameter which directly helps to compare the transient response of the topologies when a load current step occurs. In this case, on a heavy to light load step, the high step-down topology has the same slew rate as the buck ones as shown in Table 2.1.

However, when a light to heavy load step occurs, the reduced voltage excursion applied to the inductor and the limited maximum duty cycle of the high step-down converter, limit its maximum slew rate to the values shown in Table 2.1. These values can be obtained considering that the maximum duty cycle  $D_{max}$  limit allows to have a maximum slew rate over a switching period which is limited to:

$$\max \frac{di_L}{dt}\Big|_{L \to H} = \frac{\frac{\frac{V_i}{n} - V_o}{L} D_{max} T_s - \frac{V_o}{L} (1 - D_{max}) T_s}{T_s} = \frac{\frac{V_i}{n} D_{max} - V_o}{L}.$$

(2.46)

This comparison seems to be quite unfavourable for the high step-down. However, we have to consider that it is done assuming the same inductance value and switching period. As explained above, the advantages given by reduced switching losses and ripple reduction allow to relieve this condition by increasing the switching frequency and at the same time reduce the inductance value. This solution is the one followed in this work. An additional way to improve the transient response is by using coupled inductors as shown in [47]. This way the leakage inductance of the coupled inductors determines the slew rate during load variations, while the ripple reduction is determined by the coupled inductance. A detailed study on the benefit of coupling the inductors in multiphase buck is presented in Appendix A.

Another trade-off is set by the conduction losses related to the switches. If we consider the multiphase buck, this will have n times the conduction losses of the buck, as reported in table 2.1. However, if we consider the high step-down buck, we have an additional contribution of loss. This is related to the fact that the LS switches of the first n-l phases are conducting also on next phase's HS on time. This is sketched in Fig. 2.8.

Table 2.1 Comparison of different aspects between buck, multiphase buck and high step-down multiphase buck circuital topologies.

|                                      | Buck                                                   | Multiphase Buck                                                                                                                  |                 |                                                            | ep-down<br>ase buck                                                |

|--------------------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------------------------------------------|--------------------------------------------------------------------|

|                                      |                                                        | k=1 $k=2$                                                                                                                        |                 | k = 1                                                      | k = 2                                                              |

| $\frac{V_o}{V_i}$                    | D                                                      | I                                                                                                                                | )               | $\frac{D}{n}$ , $D < \frac{1}{n}$                          | $\frac{D}{n}, D < \frac{1}{2}$                                     |

| V <sub>ds max</sub>                  | $V_{i}$                                                | ī                                                                                                                                | ,<br>i          | $HS: \frac{2V_0}{n}$                                       | $\frac{1}{n}$ , $LS: \frac{V_i}{n}$                                |

| V <sub>ds on/off</sub>               | $V_i$                                                  | V                                                                                                                                | Ţi              | <u> </u>                                                   | $\frac{l_i}{n}$                                                    |

| $\Delta I_L$                         | $\frac{V_o}{L} \left( 1 - \frac{V_o}{V_i} \right) T_s$ | $\frac{V_o}{L} \left( 1 - \frac{V_o}{V_i} \right) T_s$                                                                           |                 | $\frac{V_o}{L} \Big( 1 -$                                  | $n\frac{V_o}{V_i}$ $T_s$                                           |

| $\Delta I_{\mathcal{C}_o}$           | $\frac{V_o}{L} \left( 1 - \frac{V_o}{V_i} \right) T_s$ | $\frac{V_o}{L} \left( 1 - n \frac{V_o}{V_i} \right) T_s \qquad \frac{V_o}{L} \left( \frac{n}{2} - n \frac{V_o}{V_i} \right) T_s$ |                 | $\frac{V_o}{L} \left( 1 - n^2 \frac{V_o}{V_i} \right) T_s$ | $\frac{V_o}{L} \left(\frac{n}{2} - n^2 \frac{V_o}{V_i}\right) T_s$ |

| Phases' currents auto-balance        | -                                                      | No                                                                                                                               |                 | ,                                                          | with: $I_{L3}D_3 = I_{L4}D_4$                                      |

| $\max \frac{di_L}{dt}\Big _{H\to L}$ | $-\frac{V_o}{L}$                                       | _                                                                                                                                | $\frac{V_o}{L}$ | _                                                          | $\frac{V_o}{L}$                                                    |

| $\max \frac{di_L}{dt}\Big _{L\to H}$ | $\frac{V_i - V_o}{L}$                                  | $\frac{V_i - V_o}{L}$                                                                                                            |                 | $\frac{\frac{V_i}{n^2} - V_o}{L}$                          | $\frac{\frac{V_i}{2n} - V_o}{L}$                                   |

| Switches' conduction losses          | $R_{HS}I_{HS\ rms}^2 \\ + R_{LS}I_{LS\ rms}^2$         | $n(R_{HS}I_{HSrms}^2 + R_{LS}I_{LSrms}^2)$                                                                                       |                 | $n(R_{HS}I_{HSrms}^2 + (n-1)R_{LS}I_{HS}^2)$               |                                                                    |

| Additional constraints               | -                                                      | -                                                                                                                                |                 | $f_s \gg \frac{1}{2\pi}$                                   | $\frac{1}{t\sqrt{L_xC_{ix}}}$                                      |

| Passive components                   | <i>L</i> , <i>C</i> <sub>o</sub>                       | nL,                                                                                                                              | $nC_o$          | $nL, nC_o, ($                                              | $(n-1)C_{ix}$                                                      |

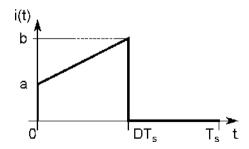

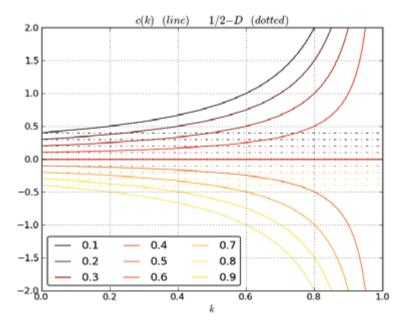

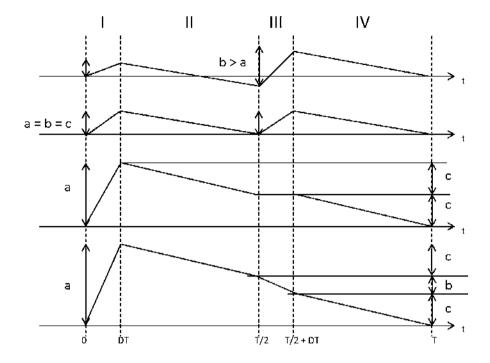

In [46] the conduction losses of the switches have been estimated approximating the inductor ripple to zero. However, this approximation is very strong, especially in our case where the output power and inductance values will assume much lower values. For this reason, we can estimate RMS current over the switches considering their effective current waveform shape which is similar to the trapezoidal pulse shown in Fig. 2.9. From this we can generically obtain that:

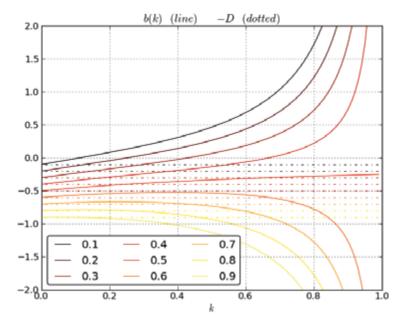

$$i|_{RMS} = \lim_{T_S \to \infty} \sqrt{\frac{1}{T_S} \int_0^{T_S} i^2(t) dt} = \sqrt{D} \sqrt{\frac{(b-a)^2}{3} + a(b-a) + a^2}.$$

(2.47)

This formula can be generalized to both HS and LS currents contributions. In fact we write it as:

$$I_{x RMS} = \sqrt{\delta} \sqrt{\frac{\Delta I_L^2}{3} + I_{L min} \Delta I_L + I_{L min}^2}$$

(2.48)

where  $\delta = D$  for the HS switches and  $\delta = I-D$  for LS ones.

Exploiting the voltage stress reduction of the high step-down switches with lower breakdown voltage can be used. These are generally providing a better  $R_{ds\ on} \cdot Q_g$  figure of merit so the increased conduction losses can be minimized. Considering an integrated implementation this effect can also be optimized by a proper sizing of the switches, in order to trade-off their conduction and switching losses.

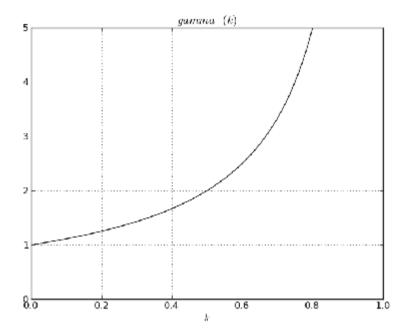

An additional constraint which should be verified with the high step-down converter is related to the constant voltage on the flying capacitors. In order to maintain this assumption it is important that the resonance frequency between flying capacitor and power inductor is at a frequency much lower that the switching one, thus:

$$f_s \gg \frac{1}{2\pi\sqrt{L_x C_{ix}}}. (2.49)$$

In conclusion, in terms of part count, the high step-down requires *n-1* additional capacitors with respect to the multiphase. Compared to other high step-down solutions proposed which involved multi-tap inductors, transformers or additional switched capacitors pre-regulators stages, this doesn't seem to be a major issue.

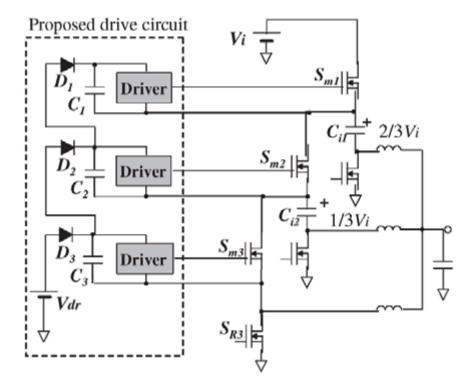

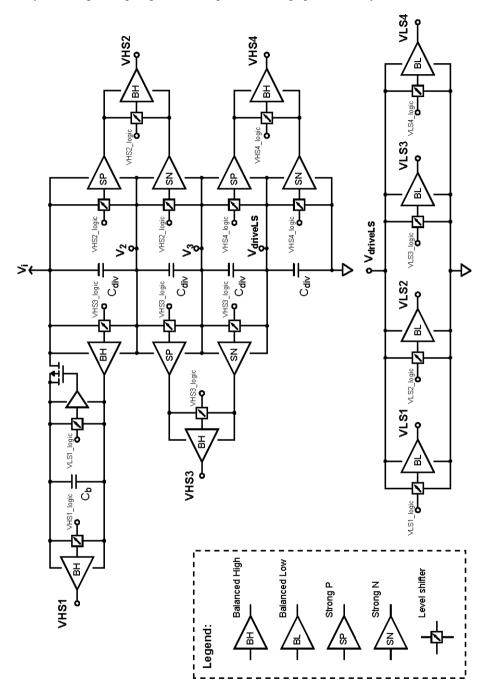

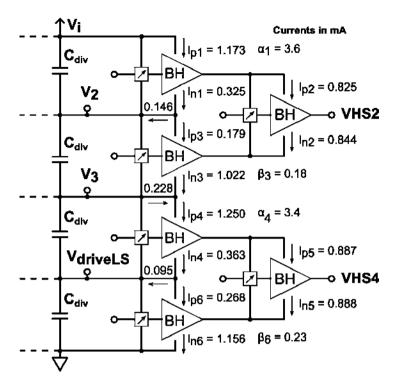

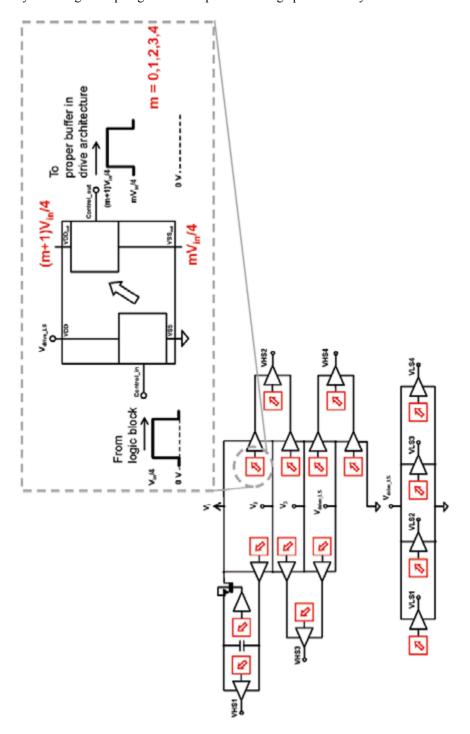

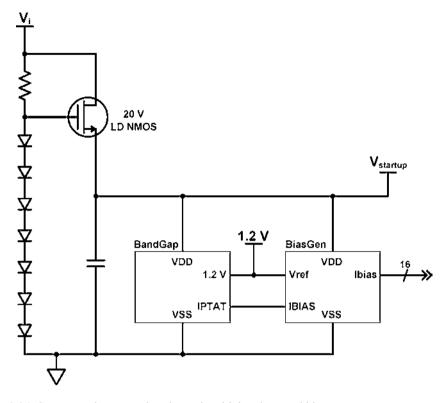

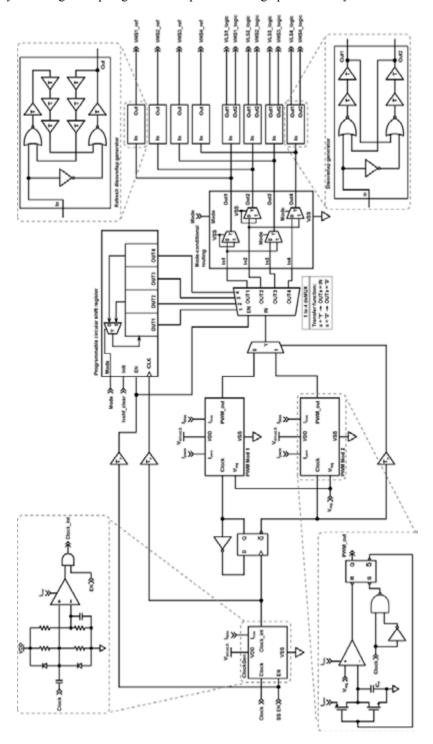

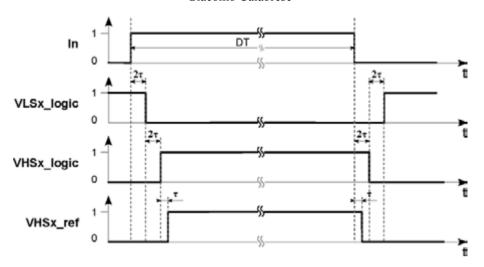

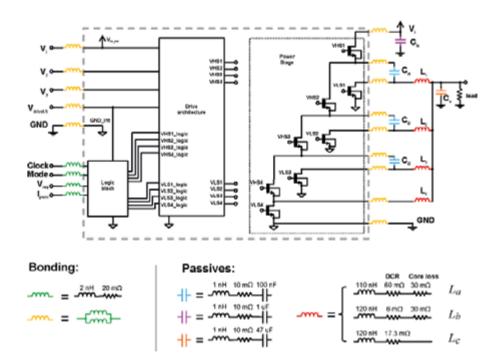

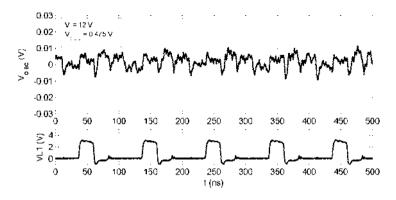

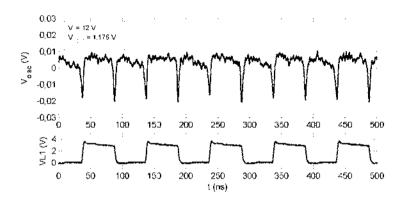

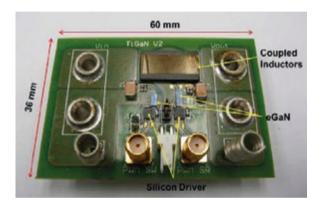

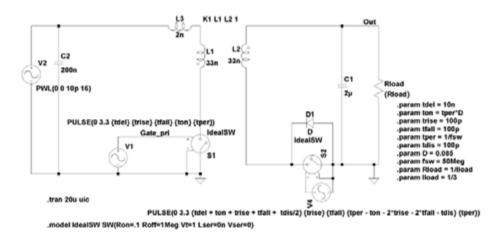

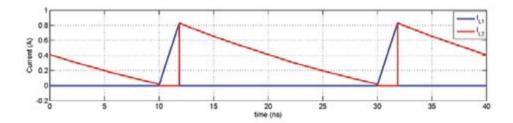

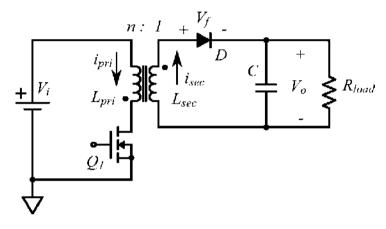

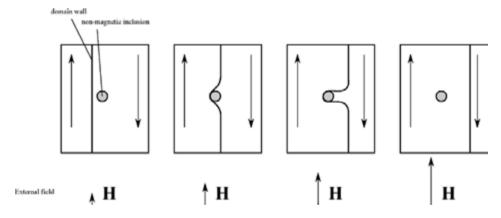

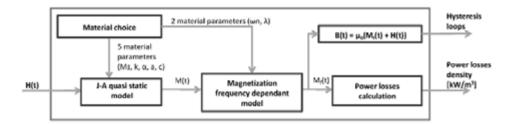

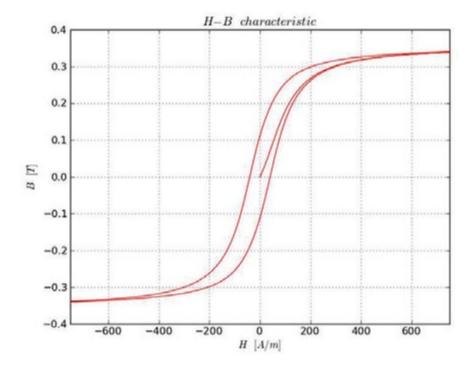

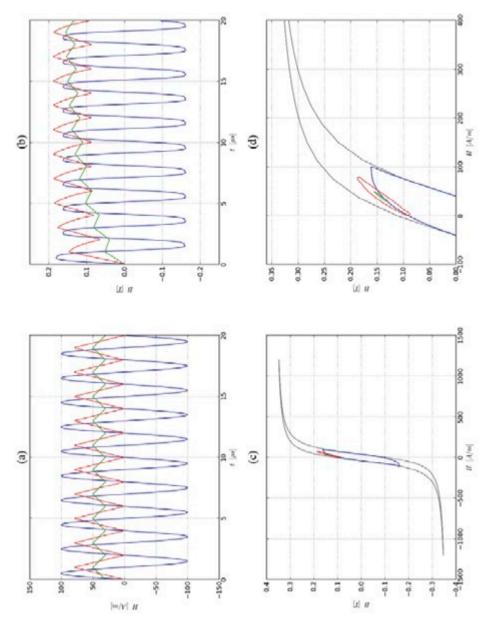

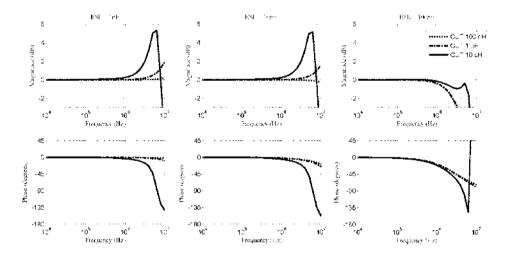

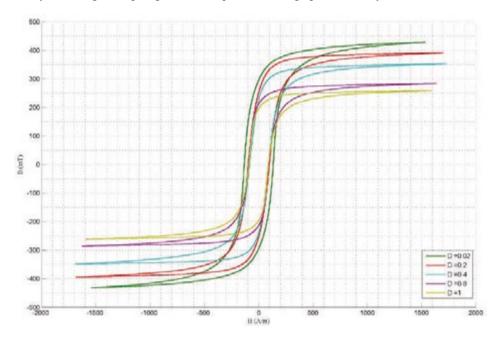

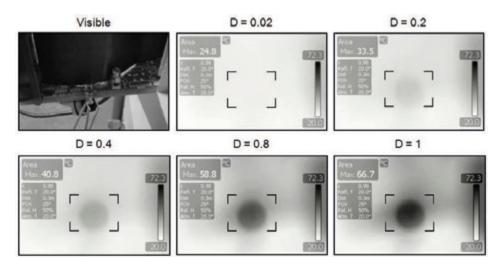

### 2.4 Functional overview of the implemented converter